资料下载

×

DSP广播级数字音频延时器设计解析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-03

音频延时器可用于广播电台直播节目。它将音频信号延时一段时间后播出,以避免主持人的口误或听众热线中听众的一些不健康言论通过广播媒体传播,从而实现直播节目的安全播出。作为广播级设备,音频延时器对动态范围、失真、信噪比和频率响应等性能指标要求很高,因此一般采用数字技术。采用计算机内置全双工声卡硬盘,可以以软件方式实现音频信号眨时,但使用操作不方便,可靠性较差,性能价格比较低。本文提出的基于高精度∑-ΔADC和DSP芯片的广播级数字音频延时器,具有性能指标高、操作简便、功能齐全等特点,该设计方案已产品化。

1 系统结构

1.1 系统构成

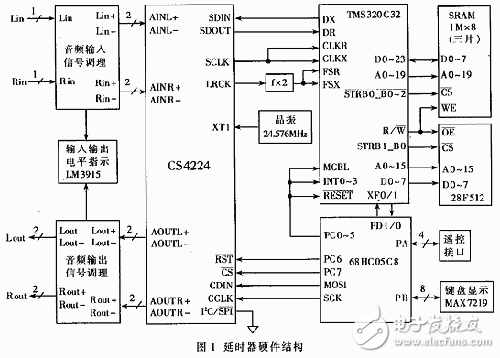

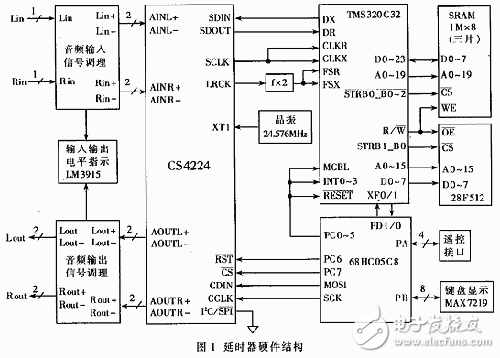

延时器硬件为主从式结构,如图1所示,主要由单睡机M发8HC05C8、DSP芯片MTS320C32和音频编解码器CS4224等组成。M68HC05C8作为整个系统的主机,完成系统的控制功能。TMS320C32作为系统的核心,完成音频信号的延时功能。CS4224及音频输入输出调理电路共同完成音频信号的A/D和D/A转换。

CS4224是高性能的24位音频编码解码器,使用∑-Δ技术提供全双工立体声数/模和模/数转换,动态范围达105dB,谐波失真和操声为-97dB,采样频率为32kHz、44.1kHz和48kHz可选。芯片采用差动输入和输出,片上自带抗混叠滤波器和输出平滑滤波器以及数字去加重滤波电路,具有模拟音量控制,支持主或从工作方式。

TMS320C32为低成本、高性能的浮点DSP芯片,非常适合语音数字信号处理。它支持24位地址总线和32位数据总线,可以寻址延时器所需的大容量存储器。它还具有串行接口,便于和串行音频数据输入输出的CS4224接口。

M68HC05C8实现人机接口,管理键盘显示和延时器遥控接口,并控制CS4224和TMS320C32的运行。

1.2 存储器接口

TMS320C32具有增强型的外部存储器接口,程序存储器的宽度可以是16位和32位,数据存储器可以是8/16/32位三种宽度。TMS320C32采用两组选通信号STRB1和STRB0,其寻址范围不同。每组选通信号由四个引脚组成,作为片选和额外的地址线,引脚的特性由每组选通信号对应的总线控制寄存器确定。通过设置总线控制寄存器的某些域,可以指定数据类型和外部存储器宽度。

延时采用了两组不同宽度的存储器。SRAM存储音频数据,设置存储器宽度为32位,数据类型为32位。由于音频编解码器CS4224为24位,因此实际使用24位,由三片8位SRAM构成,分别用STRB0_B0~2片选。FLASH芯片28F512存储用户音频信号处理程序,存储器宽度为8位,用ATRB1_B0片选。

存储器接口主要考虑存储器速度,以确定需要插入几个等待状态。由于TMS320C32时钟频率为40MHz,而FLASH存储器的存取速度为150ns,SRAM的存取速度为70ns,因此必须插入等待状态。TMS320C32具有内部可编程的软件等待状态发生器,通过STRBx控制寄存器的SWW域选择等待状态发生器的工作模式,并在WTCNT域写入需要等待的机器周期数。由于程序存储器和数据存储分别采用STRB1和STRB0选通,因此可以根据各自的存取速度分别设置所需的机器周期数。

TMS320C32具有程序引导功能。硬件复位时令MCBL/MP引脚为高电平,则工作于微计算机模式,执行片内的引导程序,将FLASH存储器中的用户程序装入内部高速RAM中运行。可以通过引脚的INT0~3确定引导模式,外部存储器装入地址根据存储器的连接方式选为Boot3区,不采用握手信号。FLASH存储器的前端为程序头,包括引导时TMS320C32必需的信息,如外部存储器宽度、引导结束后总线控制寄存器内容、各数据块长度、目标存储器宽度和数据类型等。

1 系统结构

1.1 系统构成

延时器硬件为主从式结构,如图1所示,主要由单睡机M发8HC05C8、DSP芯片MTS320C32和音频编解码器CS4224等组成。M68HC05C8作为整个系统的主机,完成系统的控制功能。TMS320C32作为系统的核心,完成音频信号的延时功能。CS4224及音频输入输出调理电路共同完成音频信号的A/D和D/A转换。

CS4224是高性能的24位音频编码解码器,使用∑-Δ技术提供全双工立体声数/模和模/数转换,动态范围达105dB,谐波失真和操声为-97dB,采样频率为32kHz、44.1kHz和48kHz可选。芯片采用差动输入和输出,片上自带抗混叠滤波器和输出平滑滤波器以及数字去加重滤波电路,具有模拟音量控制,支持主或从工作方式。

TMS320C32为低成本、高性能的浮点DSP芯片,非常适合语音数字信号处理。它支持24位地址总线和32位数据总线,可以寻址延时器所需的大容量存储器。它还具有串行接口,便于和串行音频数据输入输出的CS4224接口。

M68HC05C8实现人机接口,管理键盘显示和延时器遥控接口,并控制CS4224和TMS320C32的运行。

1.2 存储器接口

TMS320C32具有增强型的外部存储器接口,程序存储器的宽度可以是16位和32位,数据存储器可以是8/16/32位三种宽度。TMS320C32采用两组选通信号STRB1和STRB0,其寻址范围不同。每组选通信号由四个引脚组成,作为片选和额外的地址线,引脚的特性由每组选通信号对应的总线控制寄存器确定。通过设置总线控制寄存器的某些域,可以指定数据类型和外部存储器宽度。

延时采用了两组不同宽度的存储器。SRAM存储音频数据,设置存储器宽度为32位,数据类型为32位。由于音频编解码器CS4224为24位,因此实际使用24位,由三片8位SRAM构成,分别用STRB0_B0~2片选。FLASH芯片28F512存储用户音频信号处理程序,存储器宽度为8位,用ATRB1_B0片选。

存储器接口主要考虑存储器速度,以确定需要插入几个等待状态。由于TMS320C32时钟频率为40MHz,而FLASH存储器的存取速度为150ns,SRAM的存取速度为70ns,因此必须插入等待状态。TMS320C32具有内部可编程的软件等待状态发生器,通过STRBx控制寄存器的SWW域选择等待状态发生器的工作模式,并在WTCNT域写入需要等待的机器周期数。由于程序存储器和数据存储分别采用STRB1和STRB0选通,因此可以根据各自的存取速度分别设置所需的机器周期数。

TMS320C32具有程序引导功能。硬件复位时令MCBL/MP引脚为高电平,则工作于微计算机模式,执行片内的引导程序,将FLASH存储器中的用户程序装入内部高速RAM中运行。可以通过引脚的INT0~3确定引导模式,外部存储器装入地址根据存储器的连接方式选为Boot3区,不采用握手信号。FLASH存储器的前端为程序头,包括引导时TMS320C32必需的信息,如外部存储器宽度、引导结束后总线控制寄存器内容、各数据块长度、目标存储器宽度和数据类型等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章