资料下载

×

基于DSP+CPLD构架的电能质量检测装置

消耗积分:0 |

格式:rar |

大小:0.3 MB |

2017-11-14

设计了一种基于DSP+CPLD构架的电能质量监测装置,该装置利用CPLD产生DSP外围器件的控制时序,丈中详细介绍了CPLD对DSP外围器件的逻辑接口设计,通过MAX+PLUSII对CPLD的控制时序进行仿真,仿真结果验证了本设计的可行性,试验测试结果表明该装置实现了多项电能质量指标的实时在线监测。

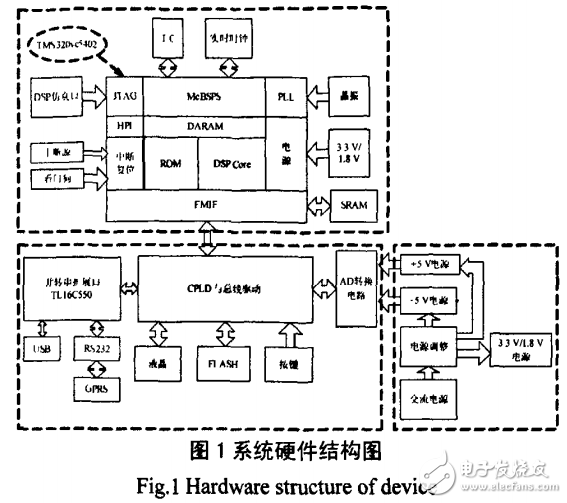

系统硬件结构设计

系统的硬件结构如图1所示。本装置的任务是完成对被监测信号的模数转换和各相电能质量指标的分析计算、存储和上传。硬件系统包括A/D转换单元、数字处理单元(DSP)、外扩程序空间(SRAM)、外扩数据储存单元(FLASH)、逻辑控制单元(CPLD)、异步通信接口单元(TLl6C550)、人机接口(按键、液晶显示)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章