资料下载

×

基于SIMD体系结构的指令级并行结构设计

消耗积分:0 |

格式:rar |

大小:1.92 MB |

2017-11-16

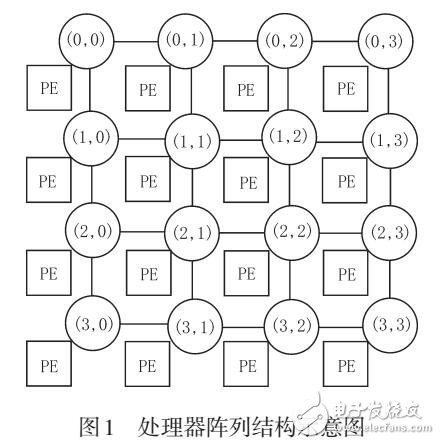

SoC的概念提出之后,随着并行计算技术与深亚微米技术进步,出现了以网络互连的大规模并行处理系统芯片( MPP SoC),即阵列处理器系统芯片( Array Processor SoC),目前系统芯片体系结构还处在发展阶段。目前多核阵列处理器( Multi-core Processor)是处理器发展的趋势。随着微电子工艺技术的不断突破,在单个芯片上能够集成越来越多的电路,为多核处理器的出现提供条件。在实现软件无线电时,多核CPU+CPU体系架构已经是经典的解决方案,通过不同的数据映射到不同的处理单元或CPU单元中,得到并行处理,提高LTE系统基带算法的执行效率。下一代通信系统中存在大量的非数据并行算法,无法通过基于指令流的大规模数据并行计算提高计算效率。要求处理器能支持指令级并行(Instruction-level Parallelism,ILP)、数据级并行(Data- level Parallelism,DLP)、线程级并行(Thread-level Parallelism,TLP)计算进行各种规则计算和不规则计算。所以为了满足新时期的用户体验,我们需要研究适用于高性能计算的多核井行处理器,具有一定的实际意义和应用价值。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章