资料下载

×

MSP430x4xx系列微控制器简介及其独特的时钟设计

消耗积分:0 |

格式:rar |

大小:0.1 MB |

2017-11-27

MSP430x4xx系列微控制器采用了FLL+时钟设计,具有功耗极低以及处理能力强、运行速度快的特点。文中首先分析 了系统的时钟与功耗之间的关系,然后重点介绍了MSP430x4xx系列FLL+的组成,同时分析了其工作原理 ,最后总结了FLL+优化系统全局性能的方法。

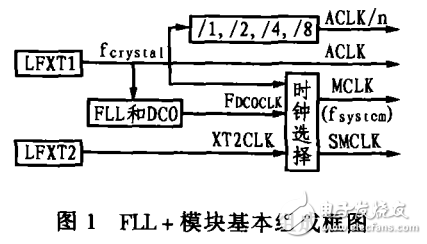

FLL+模块的组成

MSP430x4xx 系 列 的 FLL + 时 钟模块是MSP430x3xx系 列 m 结 构 的 一 种 扩 展 ,但却与MSP430xlxx系列 的 时钟 系统 有很 大 的不同 ,后者 没有 硬件 FLL,因此 ,要想 获得 较精确 的 时钟 ,需用 软件进行 DCO频率校准,这也就是所谓的“软锁频”。由于 FLL+支 持 的频率 范 围更 大 ,因而 可 以采 用 手表晶振或者高频晶振。图 1所示是 FLL.+模块的基本组成,从图中可以看出:FLL+主要由 LFXT1振荡器 、Ik‘XT2振荡 器 、DCO振 荡器 和锁频 环 以及时钟缓冲输出组成 。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章