资料下载

×

PCI Express 4.0通路裕量和其优点分析

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-11-28

当面临更高带宽和更快上市时间的要求时,设计人员将面临新的挑战。较高的数据传输速率使得更高带宽成为可能,同时它们会限制传输距离(由于信道损失增大),使信号的完整性降级,并降低制造良率。解决这些挑战需要时间和资源,这会对系统设计进度造成负面影响,更糟糕的是,在设计系统时,这类负面影响可能并不明显。

通过在接收器处引入PCI Express 4.0(PCIe 4.0)通路裕量特性,PCI-SIG正在解决该项挑战,通过引入该项特性,系统设计人员能够评估其系统的性能变化容差。通路裕量允许系统设计人员使用PCIe 4.0装置来测量每一系统中的可用电气裕量。在本文中,介绍了通路裕量特性,以及它是如何使设计人员按时交付更健壮系统的。

系统中的性能变化

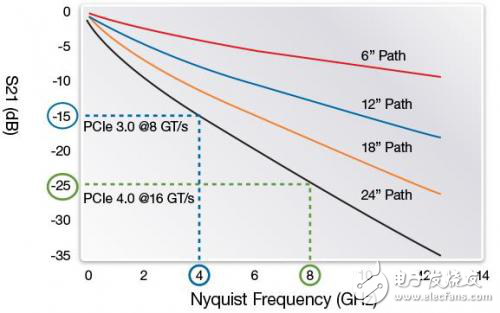

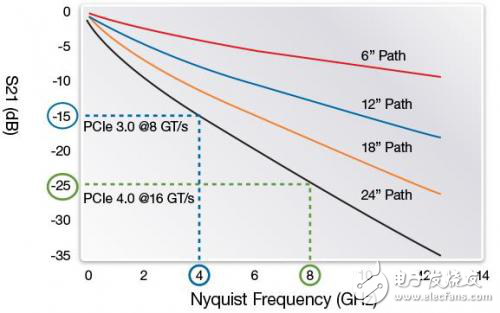

PCI Express是一种点对点互连,它支持内部和外部连通性,或是通过线缆进行,板级连接。有三种常见的板级连接情形,它们是芯片对芯片(无连接器)、单个板和连接器的扩展卡接口、以及带多个板和连接器的背板。在复杂的背板情形下,很多原因都可能会导致信号完整性降级,包括串扰、反射、不连续和信道损失。在图1中,给出了一个在FR-4印刷电路板(PCB)上的信道损失差异示例,其中,与8 GT/s PCIe 3.0相比,24英寸走线在16 GT/s PCIe 4.0下具有更高的损失。

图1:6”/12”/18”/24” FR-4 6mil条线PCB上的插入损失

由于PCB和连接器制造方面的差异,对于某一插槽中的某一卡,与运行在另一插槽上的采用不同制造的另一卡相比,会具有不同的信号性能,如图2所示。由于PCB制造变化,如板层厚度、走线宽度或走线间距,都会增大信道损失、阻抗和系统噪音。对于它们中的任一个或全部,会影响信号眼图的质量和打开尺寸。在不同厂家或来自同一制造商的不同批次之间,可看到这类PCB差异。

通过在接收器处引入PCI Express 4.0(PCIe 4.0)通路裕量特性,PCI-SIG正在解决该项挑战,通过引入该项特性,系统设计人员能够评估其系统的性能变化容差。通路裕量允许系统设计人员使用PCIe 4.0装置来测量每一系统中的可用电气裕量。在本文中,介绍了通路裕量特性,以及它是如何使设计人员按时交付更健壮系统的。

系统中的性能变化

PCI Express是一种点对点互连,它支持内部和外部连通性,或是通过线缆进行,板级连接。有三种常见的板级连接情形,它们是芯片对芯片(无连接器)、单个板和连接器的扩展卡接口、以及带多个板和连接器的背板。在复杂的背板情形下,很多原因都可能会导致信号完整性降级,包括串扰、反射、不连续和信道损失。在图1中,给出了一个在FR-4印刷电路板(PCB)上的信道损失差异示例,其中,与8 GT/s PCIe 3.0相比,24英寸走线在16 GT/s PCIe 4.0下具有更高的损失。

图1:6”/12”/18”/24” FR-4 6mil条线PCB上的插入损失

由于PCB和连接器制造方面的差异,对于某一插槽中的某一卡,与运行在另一插槽上的采用不同制造的另一卡相比,会具有不同的信号性能,如图2所示。由于PCB制造变化,如板层厚度、走线宽度或走线间距,都会增大信道损失、阻抗和系统噪音。对于它们中的任一个或全部,会影响信号眼图的质量和打开尺寸。在不同厂家或来自同一制造商的不同批次之间,可看到这类PCB差异。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章