资料下载

×

基于FPGA设计LCD显示控制器相关知识详解

消耗积分:0 |

格式:rar |

大小:1.2 MB |

2017-12-01

通过对LCD1602/LCD12864显示模块控制时序和指令集的对比分析,利用Verilog HDL描述语言完成了多功能LCD显示控制模块的IP核设计.所设计的LCD显示控制器具有很好的可移植性,只需通过端口的使能参数配置便可以驱动LCD1602/LCD12864模块实现字符或图形的实时显示,并且该多功能LCD控制器的可行性也在CvcloneII系列的EP2C5T144C8 FPGA芯片上得到了很好的验证。

2 多功能显示控制器的操作时序

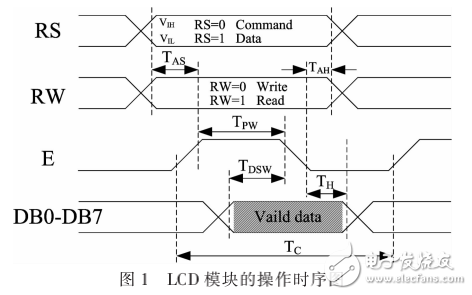

如果LCD12864液晶模块T作在并口的数据传输模式(PSB=1、RST=I)下,就和LCD1602液晶模块具有完全相同的控制时序.这就要求多功能控制器产牛的E、RW、RS控制信号具有正确的时序.LCD模块的读/写操作时序由使能信号E完成:对读/写操作的识别是判断RW信号上的电平状态:RS信号用于识别数据总线DBO-DB7上的数据是指令代码还是属于显示数据l4.61,控制信号的操作时序如图1所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章