资料下载

×

明导:转向使用即插即用的分层DFT

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-12-04

上海2013年10月24日电 /美通社/ -- 电子设计自动化技术的领导厂商 Mentor Graphics近日发布一份题为《转向使用即插即用的分层 DFT 的好处》的研究报告。

一、背景

传统的全芯片 ATPG 正日渐衰退,对于许多现有的和未来的集成芯片器件来说,一项主要挑战就是如何为庞大数量的设计创建测试图案。对于有百万门甚至数亿门的设计,传统上等到设计完成再创建测试图案的方法是不切实际的,产生所有这些图案需要庞大的计算能力和相当多的时间。分层可测试性设计通过在区块或内核上完成了 DFT 插入和图案生成解决了这个问题。这大大减少了图案生成时间和所需的计算资源。它还能让你在设计过程中提前完成大部分 DFT 和图案生成,从而大幅提高可预测性并降低风险。本文将介绍分层 DFT 流程的:插入扫描包装器 (Wrapper)、为内核生成灰盒图像,将内核级图案重定向到集成芯片顶层的简单映射步骤。

二、为什么即插即用是合理的?

即插即用这种方法带来的一个重要好处就是,在设计过程中你可以在内核层面提前完成所有工作。这降低了许多类型的风险,因为任何问题都可以提前解决,让最终芯片测试架构和结果变得更可预见。在内核层面做更多的测试工作还能让各单独的开发团队独立工作,然后向做芯片集成工作的同事交付标准的 DFT 操作和测试图案等数据。此外,一旦设计和图案数据完成,同样的数据可以被重新用于任何使用该内核的芯片设计。即插即用方法同样非常灵活。如果设计出现问题,需要进行工程更改(ECO),那么只需要对进行ECO的内核重新生成测试图案。

三、使用包装器链打造独立内核

分层和内核的即插即用方法的基本要求之一是,确保每个内核可以独立进行测试。DFT 工具可以从内核IO开始,并横穿内核逻辑直到找到第一个寄存器,然后将其包括在包装器链中。这些单元由于同时执行功能性任务和测试任务,因而被称为共享包装器单元。许多设计包含寄存器IO,这样进出内核的信号的时序能得到很好地确定。这使包装器插入变得非常简单。

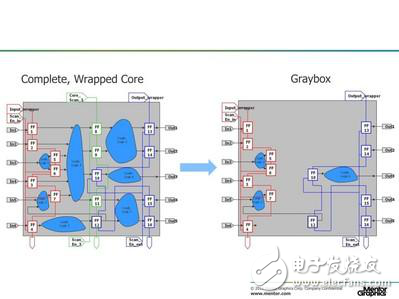

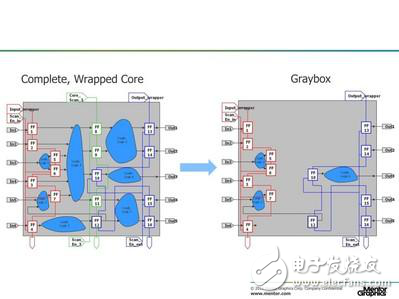

包装器链同时还支持顶层IC建模和规则检查。一旦包装器链被插入,DFT 工具程序可以分析任何内核,并找出IO和包装器链之间存在什么样的逻辑。利用该逻辑,内核的部分图像被写出,我们称之为灰盒(图1)。灰盒被用来验证内核在顶层的连接是否正确(设计规则检查),同时也被用来创建各种内核之间的简单互连测试。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

一、背景

传统的全芯片 ATPG 正日渐衰退,对于许多现有的和未来的集成芯片器件来说,一项主要挑战就是如何为庞大数量的设计创建测试图案。对于有百万门甚至数亿门的设计,传统上等到设计完成再创建测试图案的方法是不切实际的,产生所有这些图案需要庞大的计算能力和相当多的时间。分层可测试性设计通过在区块或内核上完成了 DFT 插入和图案生成解决了这个问题。这大大减少了图案生成时间和所需的计算资源。它还能让你在设计过程中提前完成大部分 DFT 和图案生成,从而大幅提高可预测性并降低风险。本文将介绍分层 DFT 流程的:插入扫描包装器 (Wrapper)、为内核生成灰盒图像,将内核级图案重定向到集成芯片顶层的简单映射步骤。

二、为什么即插即用是合理的?

即插即用这种方法带来的一个重要好处就是,在设计过程中你可以在内核层面提前完成所有工作。这降低了许多类型的风险,因为任何问题都可以提前解决,让最终芯片测试架构和结果变得更可预见。在内核层面做更多的测试工作还能让各单独的开发团队独立工作,然后向做芯片集成工作的同事交付标准的 DFT 操作和测试图案等数据。此外,一旦设计和图案数据完成,同样的数据可以被重新用于任何使用该内核的芯片设计。即插即用方法同样非常灵活。如果设计出现问题,需要进行工程更改(ECO),那么只需要对进行ECO的内核重新生成测试图案。

三、使用包装器链打造独立内核

分层和内核的即插即用方法的基本要求之一是,确保每个内核可以独立进行测试。DFT 工具可以从内核IO开始,并横穿内核逻辑直到找到第一个寄存器,然后将其包括在包装器链中。这些单元由于同时执行功能性任务和测试任务,因而被称为共享包装器单元。许多设计包含寄存器IO,这样进出内核的信号的时序能得到很好地确定。这使包装器插入变得非常简单。

包装器链同时还支持顶层IC建模和规则检查。一旦包装器链被插入,DFT 工具程序可以分析任何内核,并找出IO和包装器链之间存在什么样的逻辑。利用该逻辑,内核的部分图像被写出,我们称之为灰盒(图1)。灰盒被用来验证内核在顶层的连接是否正确(设计规则检查),同时也被用来创建各种内核之间的简单互连测试。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

图1:当扫描链插入内核,包装器链的结构允许将内核隔离为一个完整的包装器内核,如左图所示。右图显示了一个灰盒模型,其中顶层测试只需要内核IO和包装器链之间的逻辑。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章