资料下载

×

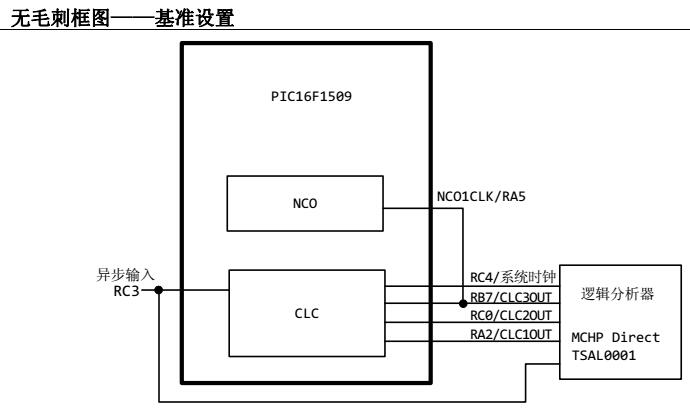

AN1451 - 采用可配置逻辑单元(CLC)实现无毛刺设计

消耗积分:2 |

格式:rar |

大小:1.63 MB |

2018-03-27

数字电路设计人员经常面临的挑战之一是要消除所设计电路的毛刺信号。为此,通常需要确保数据锁存期间具有足够的建立时间以及保持时间。

“毛刺”是不能在整个时钟周期内都保持有效的信号。带毛刺的信号如果馈送至多个锁存器的时钟线,部分锁存器可能无法更新。这无疑是设计人员要避免的情况。还应当注意传播延时会随温度而变化,因此,开发期间未产生毛刺的设计电路在其他情况下仍有可能产生毛刺。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章