资料下载

×

了解TI的PCB路由规则为基础的DDR时序规范概述

消耗积分:0 |

格式:rar |

大小:0.09 MB |

2018-04-18

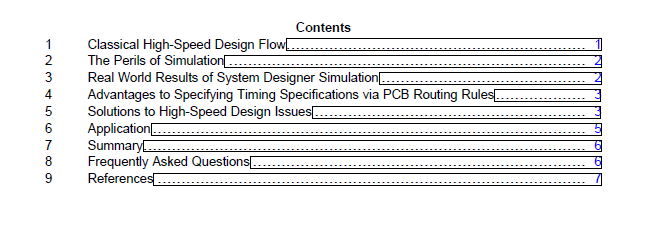

此应用报告激励DDR高速定时要求的方式。现在将被传达给系统设计师。传统的使用方法数据表参数和仿真模型是繁琐的。系统设计者使用此信息以评估是否满足和可预期的时序规范。操作可靠。最终,硬件设计者想要回答的真正问题是:“我怎么勾?”它呢?这里使用的方法不同:TI一次解决系统定时问题,然后通过直接PCB路由规则来通信解决方案。这种方法是特别适合于嵌入式JEDEC DDR内存接口,因为自然约束的系统解集和工业标准组件。

经典的高速设计流程是一个复杂的、劳动密集的事务。它需要一个广阔的人才技能集和综合仿真工具。它要求硅制造商提供漫长的时间。数据和精确的仿真模型是繁琐的开发和维护。在几乎每一个系统中,PCB必须从头开始设计。电路板的设计高速外围设备包括以下任务

·确定总线外围设备

·获取设备数据表

·获得仿真模型

·获得测试负载模型

·模拟测试负载

·设计初步的总线拓扑结构/层叠

·运行模拟

·评估信号完整性和定时的模拟

设计PCB

·运行模拟

·评估信号完整性和定时的模拟

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章