资料下载

如何使用FPGA进行图像实时处理系统的设计

由于现场实时测量的需要,机器视觉技术越来越多地借助硬件来完成,如DSP芯片、专用图像信号处理卡等。但是,DSP做图像处理也面临着由于数据存储与处理量大,导致处理速度较慢,系统实时性较差的问题。本文将FPGA的IP核内置缓存模块和乒乓读写结构相结合,实现了图像数据的缓存与提取,节省了存储芯片所占用的片上空间,并且利用图像预处理重复率高,但算法相对简单的特点和FPGA数据并行处理,结合流水线的结构,大大缩短了图像预处理的时间,解决了图像处理实时性差的问题。

1 系统架构和流程简介

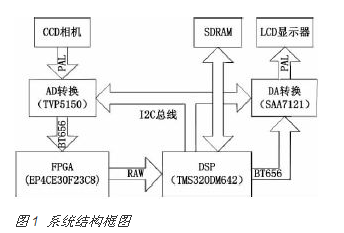

本系统采用了FPGA与DSP相结合的架构,综合了各自的优点,使系统满足实时性要求的同时,又可以在后续任务中完成复杂算法的处理。系统的整体架构如图1所示。

系统上电后,CCD 相机向AD 转换芯片TVP5150输入PAL制式模拟图像信号,TVP5150将模拟信号转换成数字信号后,以ITU-R BT656格式传输到FPGA,FPGA对采集到的ITU-R BT656格式的图像数据去消隐化后进行预处理,处理完之后传输到DM642的VP0口,VP0以8位RAW 格式接收图像数据,并通过EDMA通道存储到连接在EMIFA接口上的SDRAM 中。经过DSP的图像处理后,将SDRAM 中的图像数据以ITU-R BT656的格式经DM642 的VP2 口传输到DA 芯片SAA7121,然后SAA7121进行DA转换后,将PAL制式的模拟信号输出到LCD显示器上显示。需要说明的是,TVP5150和SAA7121通过DM642的I2C总线接口配置。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章