资料下载

如何使用FPGA实现发电机组频率测量计的设计

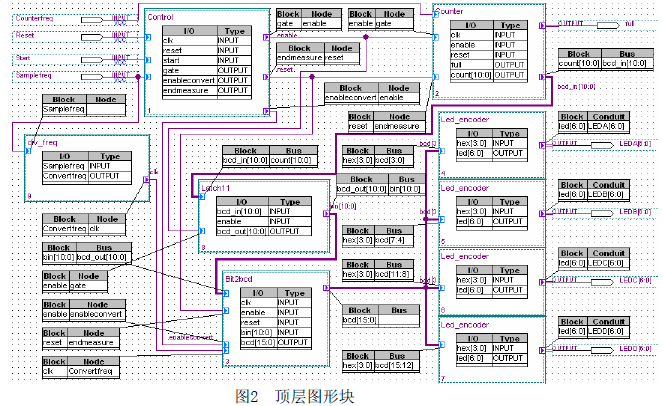

利用Verilog HDL 硬件描述语言自顶向下的设计方法和QuartusⅡ 软件,在复杂的可编程逻辑器件(FPGA, Field Programmable Gate Array)中实现了发电机组频率测量计的设计。该设计采用了光电隔离技术,提高了系统可靠性和稳定性。通过仿真,表明这种方法与传统方法设计的数字电子系统相比,便于频率测量范围的扩展,同时其可移植性强、可更改性好。

在现代社会中,电资源成为人们生活当中不可缺少的一部分,而发电机和电动机在电力系统中扮演着非常重要的角色。在很多场合,需要对电机组和电网的频率进行测量。目前,频率测量的电路系统很多,这里介绍一种数字电路测频:基于FPGA的发电机组的频率测量计。

随着电子技术的不断发展和进步,以EDA为代表的数字电路设计发生很大变化。在设计方法上,已经从“电路设计—硬件搭试—焊接”的传统设计方式到“功能设计—软件模拟—下载调试”的电子自动化设计模式。在这种状况下,以硬件描述语言(Hardware DescriptionLanguage)和逻辑综合为基础的自顶向下的电子设计方法得到迅速发展。Verilog HDL语言是目前应用最广泛的硬件描述语言,它是在C语言的基础上发展起来的,语法较为自由灵活、拥有广泛的学习群体、资源比较丰富,且容易学简单易懂。本文发电机组频率测量计的设计是在Verilog hdl语言的基础上展开的,源程序经过Altera 公司的QuartusⅡ5.0软件完成了综合、仿真(功能仿真和时序仿真),FPGA(Field Programmable Gate Array,现场可编程门阵列) 选用的是Cyclone系列的EP1C3T144C6器件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章