资料下载

如何使用FPGA和MCU进行大型LED显示屏系统设计

传统的大型LED显示屏系统以单片机MCU、ARM 或PLD为核心控制芯片,以FPGA为核心的led显示屏控制系统设计实现起来比较复杂,并且需要以高性能的FPGA芯片作为基础,而以微处理器为核心的LED显示屏控制系统不够灵活,在改变LED屏幕显示尺寸时,需要大幅修改系统设计,PLD虽在处理速度上有较大提高且能很好地控制多模块显示,但其在时序电路描述方面明显不如FPGA。提出了基于FPGA与单片机MCU的大型LED显示屏系统设计方案,该系统中FPGA为主控制单元,单片机为扫描控制单元,该方案简化电路,提高系统的灵活性和可靠性。实践仿真结果表明:系统显示内容较多,能较好地支持彩色显示,降低了功耗,实现了现场实时控制显示。

随着平板显示技术的不断更新,大型LED显示系统利用发光二极管构成的点阵模块或像素单元组成大面积显示屏,主要显示字符、图像等信息,具有低功耗、低成本、高亮度、长寿命、宽视角等优点。近年来广泛应用在证券交易所、车站机场、体育场馆、道路交通、广告媒体等场所。

通常用单一单片机作为主控器件控制和协调大屏幕显示。由多片单片机构成的多处理器系统,其中一片作为主CPU,其他作为子CPU共同控制大屏幕的显示,该系统可以减轻主CPU 的负担,提高了LED点阵的刷新频率。但单片机的驱动频率有限,无法驱动等分辨率LED屏幕,尤其是对于多灰度级彩色大屏幕,数据送到显示屏之前要进行灰度调制重现图像的色彩,对数据的处理速度要求更高,单片机控制在速度上无法满足上述要求。因此该方案主要应用于实时性要求不高的场合,主要进行一些文字、图片等静态异步显示的控制。视频图像信号频率高、数据量大,要求实时处理,采用FPGA/CPLD设计控制电路,其中的同步控制、主从控制、读写控制和灰度调制等大量电路进行了集成,简化系统结构,便于调试且系统结构紧凑,工作可靠。与单片机控制电路相比,电路结构明显简洁,电路的面积减小,可靠性增强,调试也更为简单,由于FPGA/CPLD可以并行处理多个进程,比起单片机对任务的顺序处理效率更高,点阵的刷新频率也随之提高。

对实时性要求较高、数据量较大的场合下,可编程逻辑器件是首选的核心数据处理器。本系统考虑对于传输视频数据大小和驱动LED大屏幕刷新频率的要求,LED发送卡、接收卡均采用FPGA作为核心处理器,笔者选择Xilinx公司基于90nm工艺制造的XC3S250E-FTG256,内有25万逻辑门,最高频率可以达到600MHz,完全可以满足系统速度的要求在系统中作为扫描控制单元,同时以MCU芯片为主控制单元。采用该方案可以有效简化显示屏的电路结构,从而提高了整个控制系统的灵活性和可靠性。

1 系统的组成和工作原理

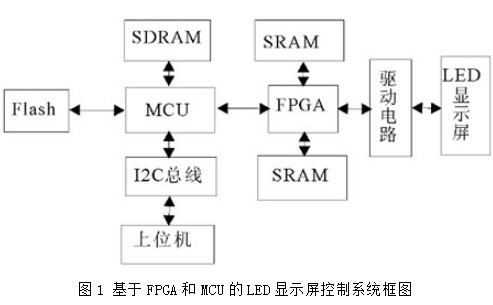

该系统采用89C51单片机和SDRAM 组成控制中心,由基于Xilinx公司的FPGA的90nm工艺制造的XC3S250E-FTG256和RAM 组成扫描控制模块,以FLASH作为存储器模块,采用以太网传输数据,组成LED屏的控制系统。系统结构如图1所示。其工作原理为:主机通过TFTP协议将图片传输给系统以太网接口模块,以太网接口模块解析协议,接收图片数据,然后将数据传输给MCU,MCU 将接收到的数据写入存储模块NAND FLASH.在显示时,MCU读取FLASH 中的数据,通过SPI接口将数据传输给FPGA扫描控制模块,经扫描控制模块处理后传输到LED屏幕上显示。

2 硬件系统设计

2.1存储器电路设计

本系统中需要用2片RAM 芯片作为缓存来存储视频数据,并以乒乓方式进行快速读写操作。目前主要有动态存储器(DRAM)和静态存储器(SRAM),SRAM 的读写时间短,静态功耗比较低,总线利用率高,它不需要刷新电路就能保存内部存储的数据,但是它的集成度较低,相同的容量占用体积大,价格较高,主要用于性能要求较高的领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章