资料下载

×

如何进行DDR2高速PCB设计和信号完整性分析的详细资料分析

消耗积分:0 |

格式:pdf |

大小:2.09 MB |

2019-03-03

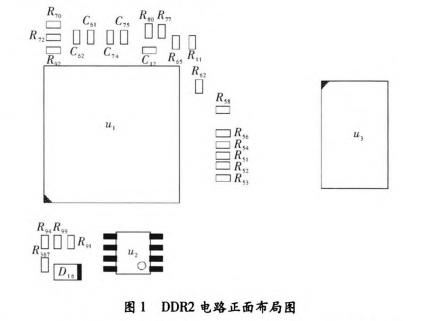

随着现代高速电路设计的发展,DDI腔.因其内存强大的预读取能力成为许多嵌入式系统的选择。然而, DDR2的仿真工作不仅繁琐耗时量大,对EMI的仿真也比较困难,给PCB设计也带来了大量的工作难点。文中针对 DDR2高速电路中存在的信号完整性问题进行了分析,提出了PCB设计要点。并以单个DDR2存储器与控制器间的 PCB设计为例,对如何在减少仿真工作的情况下成功完成一个可用的设计进行了论述。

DDR2内存强大的预读取能力使其成为许多嵌入式系统的选择,然而,由于其具有的高频与快速的上升、下降沿,给PCB设计带来了困难。PCB设计者不仅需要严格遵循通用的高速PCB布线规则,更要对系统中的各种信号完整性问题进行一一分析与解决。当然,对于电路中的问题逐个仿真是一种比较有效的方法,虽然仿真成功并不能保证设计完美,却可以排除大量的错误。但是,DDR2的仿真工作不仅繁琐耗时量大,对EMI的仿真也比较困难,特别当一些单位并没有专门的仿真人员或者项目时间紧张,逐个仿真是不切实际的。本文以单个DDR2存储器与控制器间的 PCB设计为例,讲述了如何在减少仿真工作的情况下成功完成一个可用的设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章