资料下载

×

FPGA教程之FPGA入门闪烁灯实验的详细资料说明

消耗积分:0 |

格式:rar |

大小:0.42 MB |

2019-03-29

本文档的主要内容详细介绍的是FPGA教程之FPGA入门闪烁灯实验的详细资料说明。

实验任务

让实验板上的8 个LED 周期性的闪烁。通过这个实验,熟悉并掌握采用计数与判断的方式来实现分频的Verilog HDL 的编程方法以及Quartus II 软件的使用方法和开发流程。

实验环境

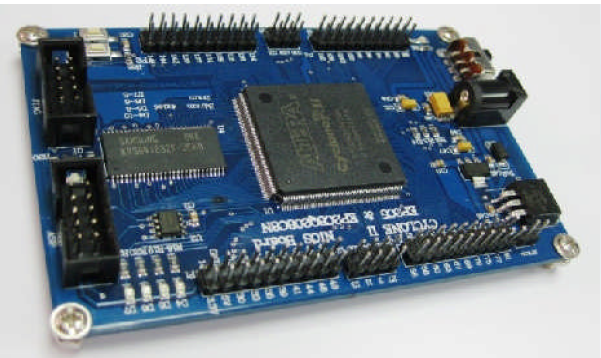

硬件实验环境为艾米电子工作室型号EP2C8Q208 增强版开发套件。软件实验环境为Quartus II 8.1 开发软件。

实验原理

艾米电子工作室开发套件板载50MHz 的时钟源,假如我们直接把它输入到发光二极管LED,由于人眼的延迟性,我们将无法看到LED 闪烁,认为它一直亮着。如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输出。本实验采用计数与判段的方式来实现降低时钟源的频率。计数电路可用计数器实现,每来一个时钟脉冲CLK,计数器就加1,而每当判断出计数器达到某个数值时,把输出状态求反,就使得8 个LED 的亮灭反转一次,即:周期性的输出高电平“1”和低电平“0”。这样设计相当于把50MHz 的时钟源分频后输出。如果最终要使得LED 1S 闪烁一次,即输出1Hz 的时钟脉冲,让计数器计到25000000 便可以让LED 亮0.5 秒、灭0.5 秒。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

xubingspdh

2019-04-17

0 回复 举报看看学习下 收起回复

xubingspdh

2019-04-17

0 回复 举报看看学习下 收起回复

- 相关下载

- 相关文章