资料下载

×

12位加法器的实验原理和设计及脚本及结果资料说明

消耗积分:2 |

格式:docx |

大小:0.13 MB |

2019-04-14

1.实验原理

加法器是数字系统中的基本逻辑器件。例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。

多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

2.设计

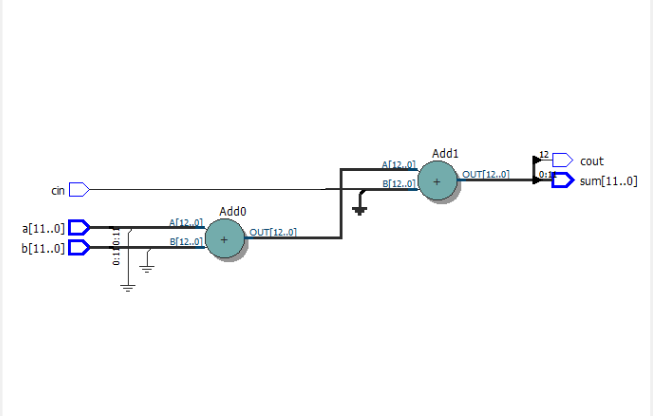

12位加法器是将3个4位加法器串行连接而形成的。如果每个4位加法器都有100ns的吞吐延迟,那么该结构的最大延迟时间将是300ns。在同步电路中,这种结构是为了使所有的操作都在同一时钟周期内进行。本文采用另一种流水线结构可以通过把该处理过程分配到多个时钟周期上,以更高的吞吐速率进行操作。速度和物理资源的折中保证了这种方法是可行的。四位全加器可对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项(Ci),以得到输出为和(S)和进位(C0)。

其中CIN表示输入进位位,COUT表示输出进位位,输入A和B分别表示加数和被加数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章