资料下载

ModelSim 10.1a版本经典教程资料免费下载

假设

对ModelSim?使用本教程基于以下假设:

您熟悉如何使用操作系统及其窗口管理系统和图形界面:OpenWindows、OSF/Motif、CDE、KDE、GNOME或Microsoft Windows XP。

您对编写设计和/或测试台的语言(如vhdl、verilog)有一定的了解。尽管modelsim是学习HDL概念和实践时使用的优秀应用程序,但本教程并不支持该目标。

在你开始之前

一些课程的准备工作留给你一些细节。您将决定在操作系统中创建目录、复制文件和执行程序的最佳方式。(当您在ModelSim的GUI中操作模拟器时,所有平台的界面都是一致的。)

示例显示Windows路径分隔符-在尝试示例时使用适合您的操作系统的分隔符。

实例设计

ModelSim附带了这些课程中使用的设计的verilog和vhdl版本。这允许您执行教程,而不管您拥有哪种许可证类型。尽管我们已经尝试最小化verilog和vhdl版本之间的差异,但在所有情况下我们都不能这样做。如果设计不同(例如,行号或语法),您将找到特定于语言的说明。请遵循适用于您所使用语言的说明。

介绍

MODESIM是VHDL、Verilog、System Verilog和混合语言的验证和仿真工具

设计。

本课简要介绍了ModelSim仿真环境的概念概述。它是

分为四个主题,您将在后续课程中了解更多。

基本模拟流程?参见第3章,基本模拟。

项目流程?参见第4章,项目。

多个库流?请参阅第5章,使用多个库。

调试工具?参考剩余课程。

下图显示了在ModelSim中模拟设计的基本步骤。

创建工作库

在ModelSim中,所有设计都被编译到一个库中。您通常通过创建一个名为“工作”的工作库来启动ModelSim中的新模拟,该工作库是编译器用作已编译设计单元的默认目标的默认库名称。

编译您的设计

创建工作库之后,您可以将设计单元编译到其中。ModelSim库格式在所有支持的平台上都兼容。您可以在任何平台上模拟设计,而无需重新编译设计。

使用您的设计加载模拟器并运行模拟

在编译了设计之后,通过调用顶层模块(verilog)或配置或实体/体系结构对(vhdl)上的模拟器,可以将模拟器加载到设计中。

假设设计负载成功,模拟时间设置为零,然后输入Run命令开始模拟。

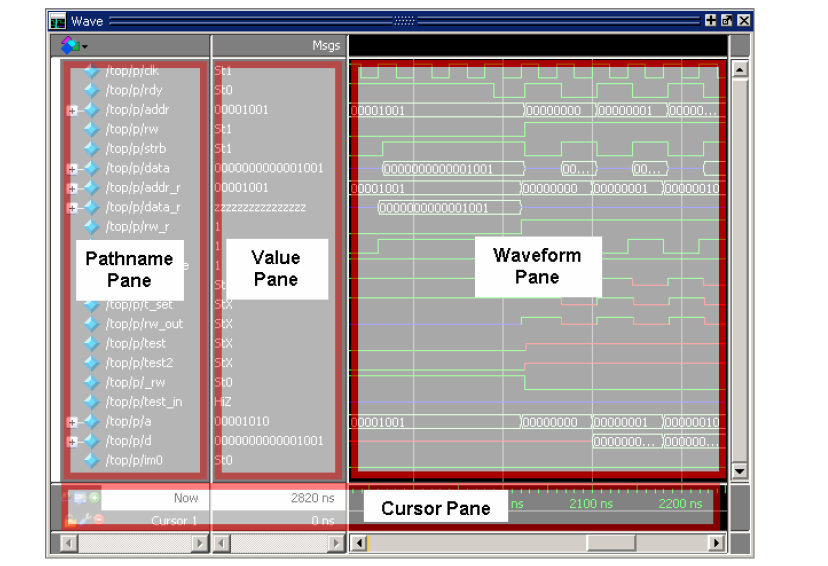

调试结果

如果没有得到预期的结果,可以使用ModelSims健壮的调试环境来跟踪问题的原因。

项目流程

项目是用于在规范或测试下进行HDL设计的收集机制。即使您不必在ModelSim中使用项目,它们也可以简化与该工具的交互,对于组织文件和指定模拟设置非常有用。

下图显示了在ModelSim项目中模拟设计的基本步骤。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章