资料下载

三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料

本文档的主要内容详细介绍的是三态门原理HDL语言DSP和ARM总线的仿真及Modelsim使用教程资料主要内容包括了:1 ModelSimSE的使用流程,2 一个Verilog计数器仿真详细流程附源代码,3 一个VHDL计数器仿真详细流程附源代码,4 Force和run两个cmd指令详细解释,5 Do文件的使用和编写例子,6 网上下载ModelSimXE调试Verilog TestBench的一个例子,HDL语言的INOUT端口仿真暨三态门仿真,VerilogHDL 的三态门实现与仿真,ARM 总线的三态门实现与仿真

三态门是FPGA 编程开发中经常遇到的一个问题。一个典型的应用就是TI 的DSP 的EMIF 总线。针对HDL 语言的三态门应用示例和仿真示例在网上很多,但是往往只讲述一种语言的,没有给予两种语言下三态门的一个综合评述,如讲述二者使用、仿真时的区别等。特别是VerilogHDL 语言下的三态门仿真,很多讲述都是语焉不详,包括使用Force 语句等,这些使用人手工干预的仿真方法明显违背了EDA 自动化的宗旨,是使用者对其仿真方法不明确的情况下的一种权益之计。

本文将使用一个DSP EMIF 接口逻辑的例子,详细讲述:

(0)什么叫做Z 态?三态的晶体管级实现是怎样的?

(1)VHDL 语言下同步、异步三态门的实现和仿真;

(2)VerilogHDL 语言下同步、异步三态门的实现和仿真;

(3)Verilog 下ARM 三态总线的仿真实例;

(4)综述两种语言下仿真的要点。

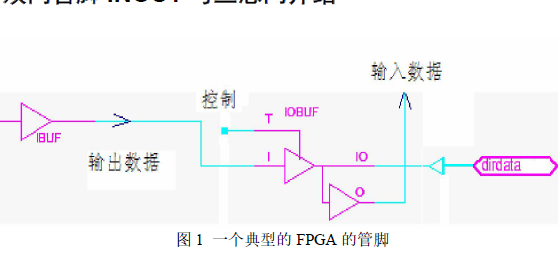

由图1 可以看出,一个FPGA 的管脚由一个输入缓冲器和一个三态输出缓冲器构成。三态输出缓冲器,即三态门,是指逻辑门的输出除有高、低电平两种状态外,还有第三种状态——高阻状态的门电路。高阻态相当于隔断状态(电阻很大,相当于开路)。 三态门都有一个EN 控制使能端,来控制门电路的通断。 可以具备这三种状态的器件就叫做三态。准确来讲,三态的高阻态(Z 态)指的就是门的输出脚的两个驱动TTL 或MOS 管都处于截止状态时的输出状态。参考图2、图3 和图4 有更详细的理解。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章