PLL/VCO技术如何提高性能、减小尺寸并简化设计周期

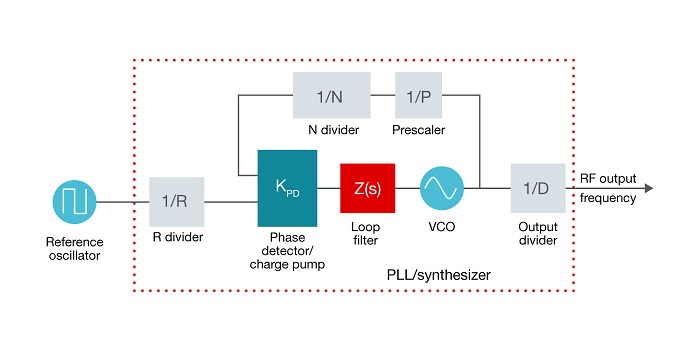

驱动高压锁相环频率合成器电路的VCO

为什么完全集成的转换环路器件可实现最佳的相位噪声性能

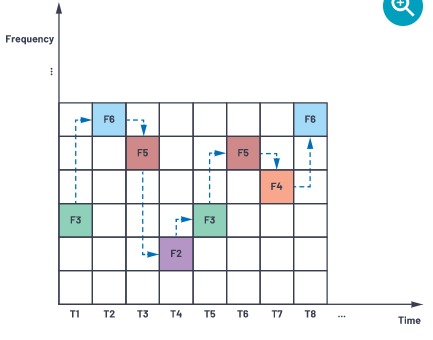

下一代软件定义无线电收发器在跳频方面取得巨大进步

HMC834LP6GE压控振荡器介绍

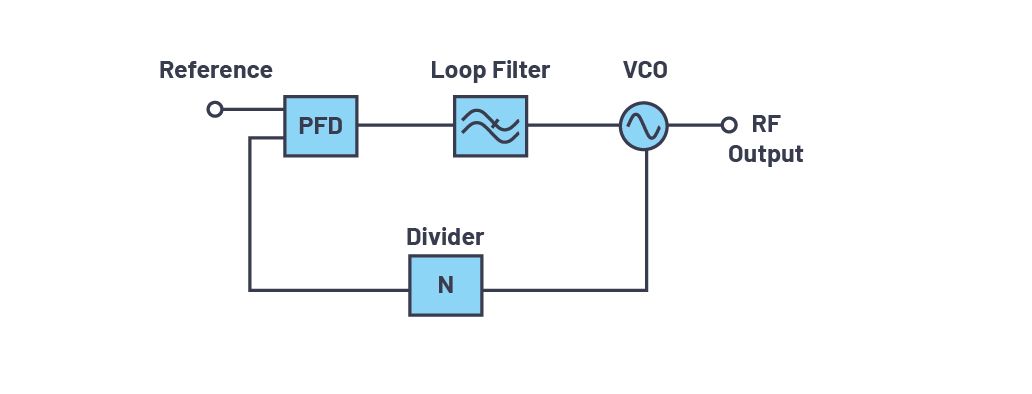

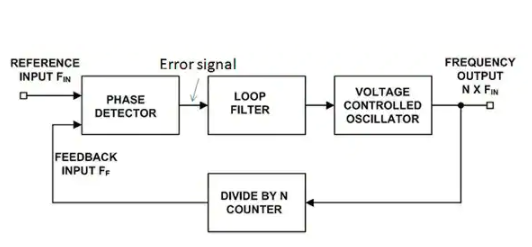

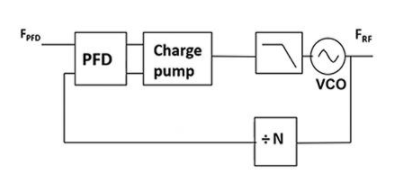

一文了解锁相环原理及工作方式

一种FLL辅助PLL的GNSS接收机矢量跟踪环路

时钟设计技巧

PLL为什么是这么一个结构呢?

AT32F403A/407时钟配置指南

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析

基于PLL和DDS的高性能频率合成器设计

jitter的关键术语和参数

详解锁相环 (PLL)电路、信号、模块组成

为什么组件集成对天基PLL合成器很重要

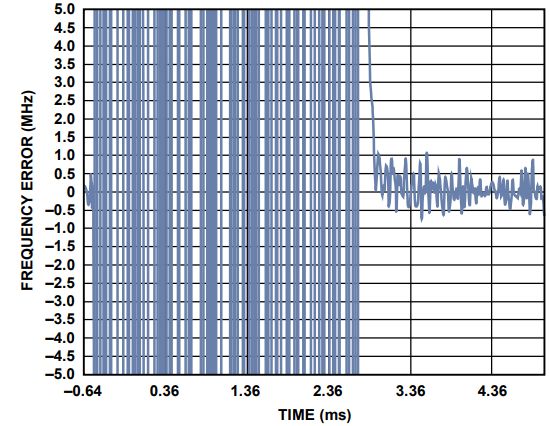

如何手动选择频段以缩短PLL锁定时间

传统 PLL 与平移环系统级封装技术

i.MXRT1xxx系列MCU时钟相关功能引脚作用

马达电机驱动器四大要点概述

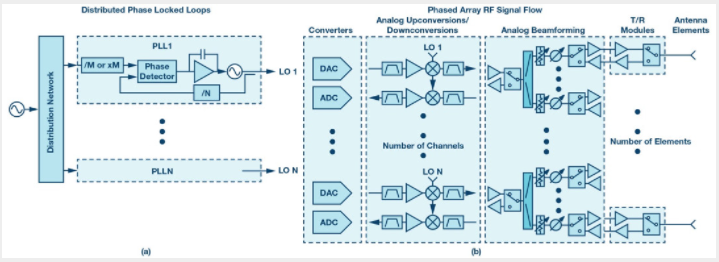

具有分布式PLL的相控阵的系统级本地振荡器相位噪声模型