资料下载

高速ADC时钟抖动的影响的了解

了解高速ADC时钟抖动的影响将高速信号数字化到高分辨率要求仔细选择一个时钟,不会妥协模数转换器的采样性能(ADC)。

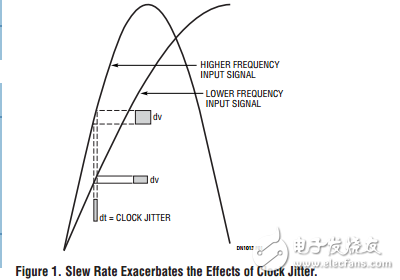

在这篇文章中,我们希望给读者一个更好的了解时钟抖动及其影响高速模数转换器的性能。作为一个例子,我们将突出最新的高性能ADC的线性技术,16位,160mspsltc2209。该ADC具有信号噪声比(SNR)77.4db与100dB SFDR的,整个的基带区。像大多数高速ADC的今天市场上的ltc2209采用采样保持(S / H)基本上需要ADC输入的快照的电路在一瞬间。当S和H开关关闭,ADC输入端的网络连接到采样电容。在开关打开的瞬间一个半时钟周期后,电容器上的电压被记录并举行。变化的时间开关打开称为光圈不确定,或抖动,并会导致误差电压成正比的抖动和输入信号摆幅率。换言之,输入频率越大振幅越大,你就越容易抖动时钟源。图1演示了这种关系摆率成比例抖动。

描述时钟为“低抖动”已成为几乎无意义的。这是因为它意味着不同的事情对不同利益集团。对于可编程逻辑供应商30ps甚至50ps是低抖动。高性能的ADC需要一个时钟1ps视《《输入频率上。更确切地说,光谱功率采样信号的分布是决定因素,相对于简单的最高频率分量除非频谱上端的满刻度信号预计。对于一个简单的例子,一个统一的乐队从DC到1MHz,功率为6dB不敏感比单音,或一个窄频带,与在1MHz等效功率。有各种各样的贡献,在任何情况下抖动,振荡器扩展到任何分频器,时钟缓冲器和由于耦合而产生的任何噪声的影响,除了内部光圈抖动的ADC本身。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章