资料下载

×

用于实现和评估TMR方法的自动快速可综合Verilog代码生成器工具介绍

消耗积分:2 |

格式:pdf |

大小:0.97 MB |

2020-04-16

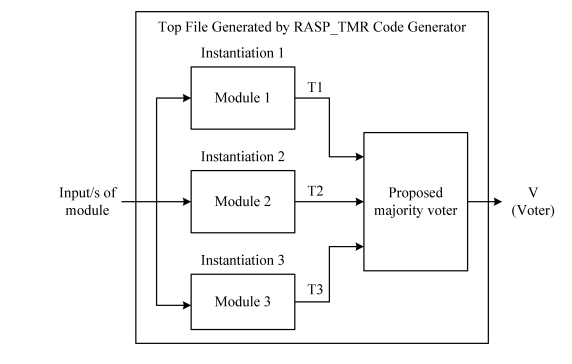

三模冗余(TMR)技术是FPGA设计中最著名的错误掩蔽和单事件效应(SEE)保护技术之一。这些FPGA设计大多采用硬件描述语言,如Verilog和VHDL。TMR技术包括设计模块的三倍化和为每个输出端口添加多数表决电路。构建这种三重化方案是一项非常重要的任务,需要花费大量的时间和精力来修改设计代码。本文开发了RASP-TMR工具,该工具具有以可综合的Verilog设计文件为输入,对设计进行解析和三次复制的功能。该工具还生成了一个顶层模块,其中所有三个模块都被实例化,并最终添加了提议的多数投票电路。该工具以其图形用户界面在MATLAB中实现。该工具简单、快速、用户友好。该工具生成可综合设计,便于用户评估和验证基于FPGA的系统的TMR设计。使用Xilinx ISE工具和ISim模拟器创建了一个仿真场景。在模拟过程中,对不同的故障模型进行了检验,如位翻转和卡死在1/0。使用各种基准测试设计的结果表明,该工具生成了可综合的代码,并且所提出的多数投票逻辑完美地掩盖了错误/失败。故障注入;容错;可靠性;单事件效应;三模冗余;Verilog-HDL

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章