资料下载

如何使用EDA实现降低芯片功耗的设计

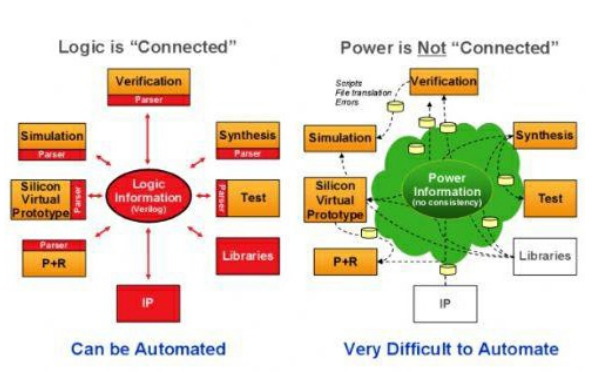

如何降低芯片功耗目前已经成为半导体产业的热点问题。过去,对于集成器件制造商(IDM)来说,最直接的作法就是通过先进的制程工艺和材料比如低K介质来解决,低功率设计可以通过将自己设计团队的技能和经验进行结合而实现。然而,当进入90nm后,漏电流问题日益凸现,CMOS静态功耗骤增,功率管理开始成为一个重要的考虑因素。这种情况在 65nm与45nm以下将更为严重,因为工艺节点的不断缩减导致栅极氧化层厚度越来越薄,栅极泄漏呈指数增长,最终动态功耗等于亚阈值泄漏电流,也等于栅极泄漏电流。这就迫使业界必须从IC的设计端就开始采用低功耗设计技术。为了应对这些挑战,设计工程师们开始提倡采用复杂的时钟门电路开关方案,从而减少了不必要的门电路开关操作。如今,为了满足功率方面的目标,设计人员运用了各种先进的低功率设计技巧,包括多阈值设计、多电压设计、动态频率电压缩放(DVFS)、时钟门控、可感知功耗的内存以及功率门控等等。在设计早期进行有效的功率评估毋庸置疑,在产品成功因素中,面市时间是重要因素之一,有时甚至决定着产品的成败。因此在设计早期解决潜在低功耗问题对于提高生产率是至关重要的。 Synopsys公司资深顾问工程师李昂表示,在设计早期(即系统架构阶段)评估系统层面低功耗的策略和代价对于后面的实现非常重要。在这阶段评估的低功耗策略主要应注意的方面包括:系统软硬件的划分、是否采用多电压(multi-voltage)、是否采用电源关断(multi-supply)、采用片上还是片外电源管理、低功耗IP的选择等。在这阶段的评估,一方面是通过对过往系统的评估经验,一方面可以通过快速原型设计,通过Eclypse系统对设计原型进行功耗估算,以评价设计的代价和功耗节省的效果。 Cadence公司高级技术主管Brad Miller也表达了相同的观点。他表示,以下五个方面将确保设计者高效而精确的达到他们的目标:1、确定设计中耗费功率的元器件;2、采用精确的开关行为数据;3、生成开关行为时考虑仿真模式;4、采用精确的线路模型;5、采用表示最坏情况功率的库。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章