资料下载

×

Xilinx7系列FPGA IO资源的逻辑资源

消耗积分:0 |

格式:rar |

大小:0.21 MB |

2020-12-29

本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

I/O逻辑资源主要包含5部分:

1, ILOGIC

ILOGIC即输入信号处理逻辑,紧挨着IOB,外界的输入信号最先经过的就是ILOGIC。ILOGIC是由许多的数据选择器和一个IDDR(input

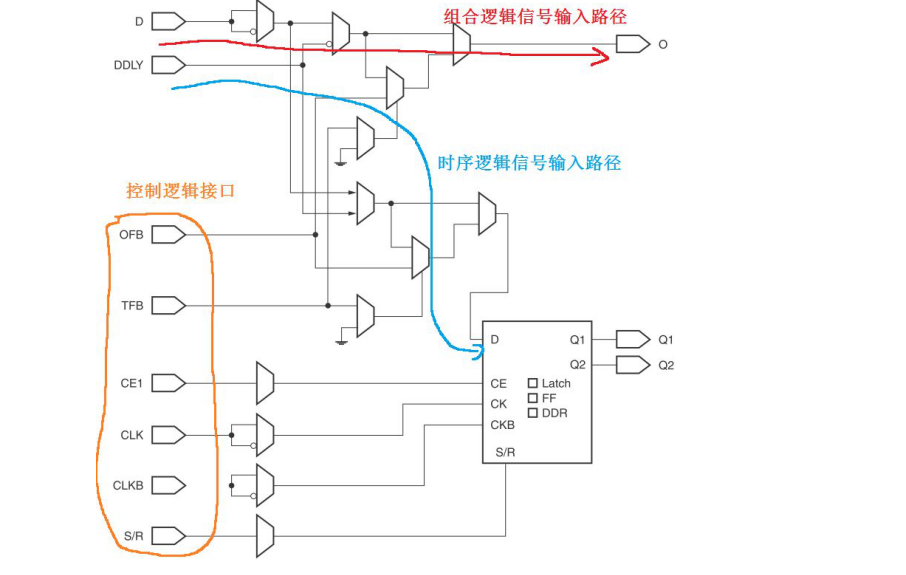

Double data rate)触发器构成。该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3。图3给出了ILOGICE3的示意图:

2, IDELAY

IDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。对于一些需要对齐的输入信号来说,这至关重要。在7系列FPGA中,它被称为IDELAYE2。IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且每节的延迟精度约为78ps(1/(32×2×FREF),FREF为IDELAYCTRL的参考时钟)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章