资料下载

×

FPGA Verilog教程的学习课件免费下载

消耗积分:0 |

格式:rar |

大小:0.30 MB |

2021-02-05

Verilog HDL是一种用于数字逻辑电路设计的语言:

- 用Verilog HDL描述的电路设计就是该电路

的 Verilog HDL模型。

- Verilog HDL 既是一种行为描述的语言也

是一种结构描述的语言。

这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

系统级(system): 用高级语言结构实现设计模块的外部性能的模

算法级(algorithmic): 用高级语言结构实现设计算法的模型。

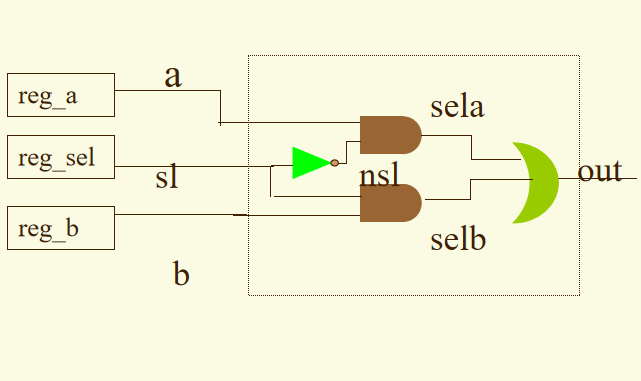

RTL级(Register Transfer Level): 描述数据在寄存器之间流动和如何处理这些数据的模型。

门级(gate-level): 描述逻辑门以及逻辑门之间的连接的模型。

开关级(switch-level): 描述器件中三极管和储存节点以及它们之间连接的模型。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章