资料下载

如何使用FPGA实现图像缩放算法的研究设计

Scaler是平板显示器件(FPD,Flat Panel Display)中的重要组成部分,它将输入源图像信号转换成与显示屏固定分辨率一致的信号,并控制其显示在显示屏上。本文在研究图像缩放算法和scaler在FPD中工作过程的基础上,采用自上而下(Top.down)的设计方法,给出了scaler的设计及FPGA验证。该scaler支持不同分辨率图像的缩放,且缩放模式可调,也可以以IP core的形式应用于相关图像处理芯片中。

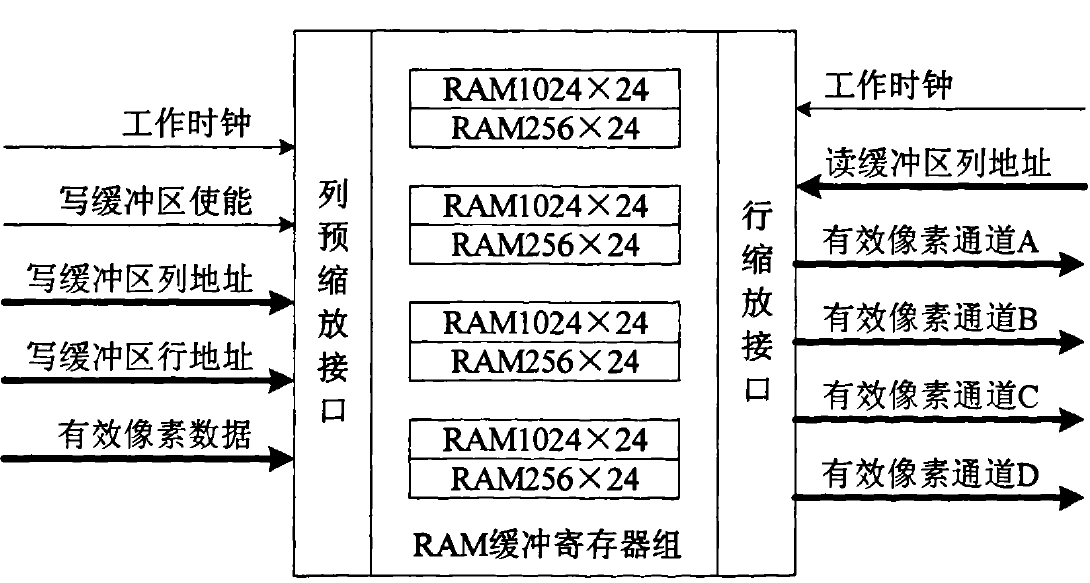

图像缩放内核是scaler的核心部分,它是scaler中的主要运算单元,完成图像缩放的基本功能,它所采用的核心算法以及所使用的结构设计决定着缩放性能的优劣,也是控制芯片成本的关键。因此,本文从缩放内核的结构入手,对scaler的总体结构进行了设计;通过对图像缩放中常用算法的深入研究提出了一种新的优化算法——矩形窗缩放算法,并对其计算进行分析和简化,降低了计算的复杂度。FPGA设计中,采用列缩放与行缩放分开处理的结构,使用双口RAM作为两次缩放间的数据缓冲区。使用这种结构的优势在于:行列缩放可以同时进行,数据处理的可靠性高、速度快:内核结构简单明了,数据缓冲区大小合适,便于设计。此外,本文还介绍了其他辅助模块的设计,包括DVI接口信号处理模块、缩放参数计算与控制模块以及输出信号检测与时序滤波模块。

本设计使用Verilog HDL对各模块进行了RTL级描述,并使用Quartus II 7.2进行了逻辑仿真,最后使用Altera公司的FPGA芯片来进行验证。通过逻辑验证和系统仿真,证明该scaler的设计达到了预期的目标。对于不同分辨率的图像,均可以在显示屏上得到稳定的显示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

chenlance2979

2021-05-31

0 回复 举报承接fpga和芯片开发项目, 免费分享技术资料2T云盘, +VX: www8928 收起回复

chenlance2979

2021-05-31

0 回复 举报承接fpga和芯片开发项目, 免费分享技术资料2T云盘, +VX: www8928 收起回复

- 相关下载

- 相关文章