资料下载

×

如何使用FPGA实现高分辨实时监控图像缩放的设计

消耗积分:0 |

格式:rar |

大小:未知 |

2021-02-05

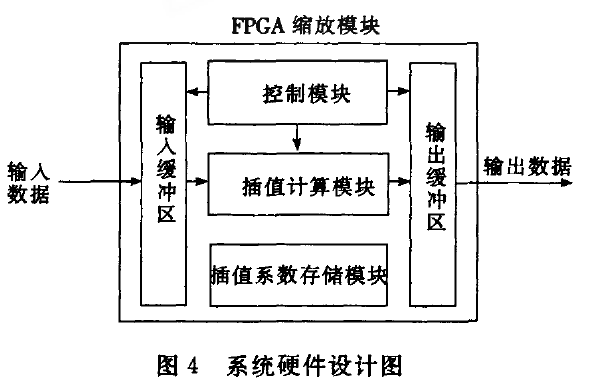

介绍了一种基于图像的双三次线性插值缩放算法的设计方法,并通过FPGA验证了设计的可行性。重点讨论了视频缩放的插值算法,对两种实现方法在硬件资源利用率及实施效率方面进行了比较并论证了块状插值实现方法的优越性。最终设计实现了高分辨率实时视频图像的缩放。

实时视频图像的监控现在已在很多领域得到应用。近年来,现场可编程门阵列(Field Pro—grammable Gate Array,FPGA)在实时图像处理中的应用越来越多。一些FPGA器件不仅提供了丰富的逻辑资源,还提供了硬件乘法器和大量的片上存储器,为实现高性能的高效率数字信号处理功能提供了方便,而在FPGA设计过程中需要对FPGA的优化设计加以考虑。

图像插值是图像处理的一个基本问题计算机图像处理、图像渲染、医用图像的重构都需要使用到图像插值。常用的图像插值方法包括最近临插值、双线性插值、双三次插值以及B样条插值等。

本文介绍了一种基于图像的双三次线性插值缩放算法的设计方法,并通过FPGA验证了设计的可行性,实现了高分辨率实时视频图像的缩放。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章