资料下载

来自Digilent设计大赛的逻辑分析仪项目

描述

目前的项目包括一个逻辑分析仪的设计,它可以帮助学生和工程师验证数字硬件、数字通信和软件集成。逻辑分析仪通常有 34 到 136 个通道,每个通道都是一个数字信号,采样频率高达 700 MHz,记录存储器高达 64 MB。它不测量电压值等模拟细节,而是检测逻辑阈值的电平。

这种设计很简单,最多可记录 8 个通道,采样频率高达 12 MHz,记录存储器高达 128 B。它适合相对较小且便宜的 FPGA,并且可以在内部实现以开发数字和微控制器应用程序。采集的数据可以通过串行接口传输到计算机。

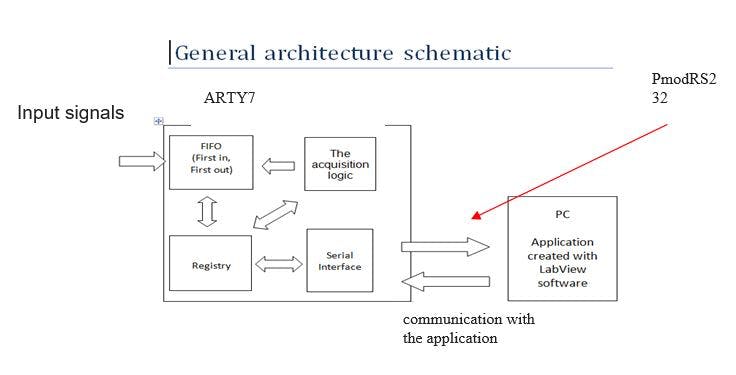

一般框图

FIFO 内存块有一个 128 字节宽的内存,用于临时存储从

输入。8 个与门让输入信号到达 FIFO 存储器。一个 2:1 多路复用器从 FIFO 存储器或状态寄存器中选择将哪些数据发送到传输模块。

数据接收寄存器是一个 11 位移位寄存器,用于逐位存储来自计算机的输入字。它被初始化为 0,当由传输时钟提供时钟时,它会移位数据,直到存储所有 11 个 RS232 输入位。

采样率发生器允许通过软件选择 12 个预定义的采样率。它们是从 ARTY 板上可用的 12MHz 振荡器开始,通过不同的可编程因子(1、2、3、4、6、12、24、120、240、1200、2400、12000)分频获得的。采样率通过 LabView 应用程序的 RS232 接口进行编程。在这个模块中,它还包括用于波特率时钟的分频器 (625)。

获取块对获取的字节数进行计数,并在达到预设数量(16、32、64 或 128)时停止处理。它在启动条件为真后对采集时钟脉冲进行计数:触发事件或软启动。

The transmission blockis used to send data over RS232. It uses the same settings as for reception (11 bits with 8 data bits and 2 stopping bits). The data byte is parallel loaded into the shift register and start bit and stop bits are added. Data is shifted on each baud rate clock pulse. The process stops after 11 clocks.

The register blockincludes 5 registers: The address register (reg_adr), the acquisition register (regrk), the Command register (reg_comanda), the Control register (reg_control) and the Status register (reg_stare). The Address register is loaded with the address of the register being written or read. The Acquistion register starts the acquisition by software or clear the data. The Command register programms the number of samples being acquired and the sampling rate. The Control register

编程触发斜率和模式。状态寄存器显示有关分析仪状态的信息(采集结束、设备复位和 FIFO 为空)

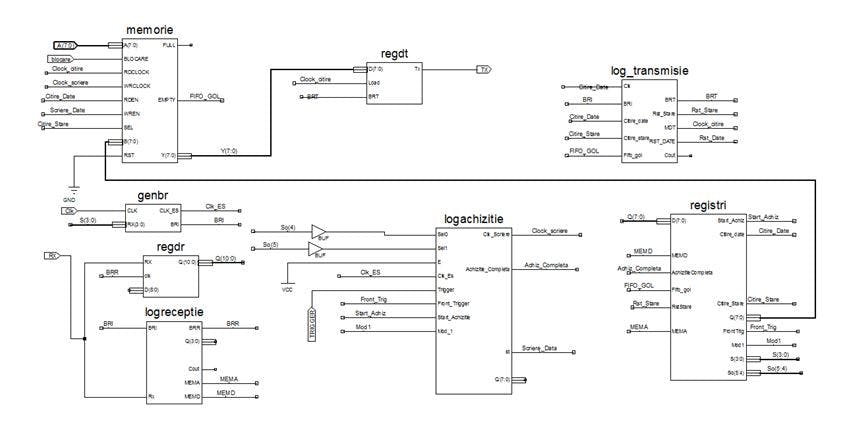

硬件设计

在项目下方的部分中找到所有项目详细信息和源文件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章