资料下载

Xilinx UltraScale:为您未来架构而打造的新一代架构

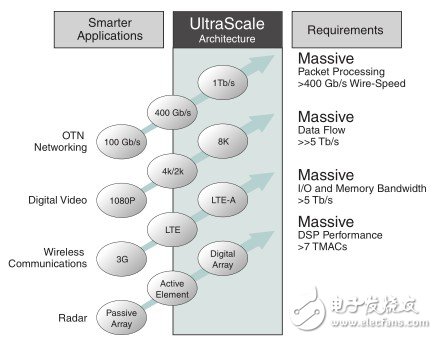

Xilinx UltraScale™ 架构针对要求最严苛的应用,提供了前所未有的ASIC级的系统级集成和容量。

UltraScale架构是业界首次在All Programmable架构中应用最先进的ASIC架构优化。该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同 时还能从单芯片扩展到3D IC。借助Xilinx Vivado®设计套件的分析型协同优化,UltraScale架构可以提供海量数据的路由功能,同时还能智能地解决先进工艺节点上的头号系统性能瓶颈。 这种协同设计可以在不降低性能的前提下达到实现超过90%的利用率。

UltraScale架构的突破包括:

• 几乎可以在晶片的任何位置战略性地布置类似于ASIC的系统时钟,从而将时钟歪斜降低达50%

• 系统架构中有大量并行总线,无需再使用会造成时延的流水线,从而可提高系统速度和容量

• 甚至在要求资源利用率达到90%及以上的系统中,也能消除潜在的时序收敛问题和互连瓶颈

• 可凭借3D IC集成能力构建更大型器件,并在工艺技术方面领先当前行业标准整整一代

• 能在更低的系统功耗预算范围内显著提高系统性能,包括多Gb串行收发器、I/O以及存储器带宽

• 显著增强DSP与包处理性能

赛灵思UltraScale架构为超大容量解决方案设计人员开启了一个全新的领域。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

-

wall675

2013-10-31

0 回复 举报同意樓上 收起回复

wall675

2013-10-31

0 回复 举报同意樓上 收起回复

- 相关下载

- 相关文章