资料下载

Powering DDR Memory

Powering DDR Memory

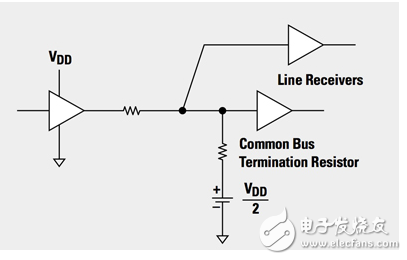

廉价的双数据速率(DDR)内存制造(以及后来的变种如DDR2和DDR3)提供了在台式机和笔记本电脑的工作记忆的主体。通过对脉冲串的上边缘和后沿时钟进行存储,内存吞吐量增加了一倍,功耗仅略有增加。然而,为了最大限度地利用这种吞吐量,避免这种高频方案的常见问题,例如,可能会无意中触发逻辑设备的振铃和反射,总线终端电路需要自己的电源。为了有效地工作,这种电源必须能提供主存储器芯片组电源的一半的输入电压,同时能够同时提供电源和接收器电流。

本文介绍了DDR内存电源的独特要求,然后研究了一些主要的电源控制器,以减轻设计工程师的挑战。

Special requirements for DDR

Figure 1 illustrates a popular termination scheme for a computer clock distribution network designed to prevent spurious ringing and reflection that could inadvertently trigger logic devices attached to the bus. An additional advantage of this topology is that it halves the power dissipated in the clock network (when the bus is high half the time and low at other times) compared to simply terminating the line via a resistor straight to ground. The trade-off is the requirement for an additional power supply to generate VDD/2.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章