资料下载

×

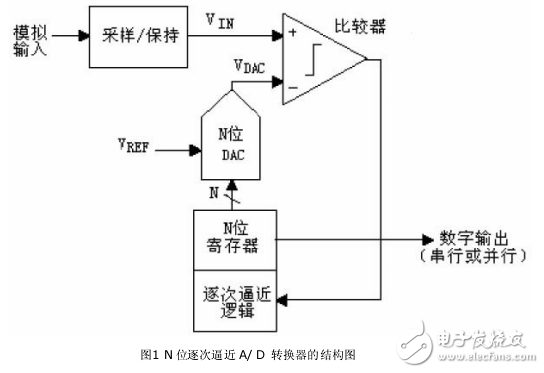

18位模数转换器的电路设计

消耗积分:0 |

格式:rar |

大小:0.50 MB |

2017-09-06

本文对逐次逼近型模数转换器(SARADC)的结构进行了介绍,并对影响ADC性能的主要因素加以分析。设计了一种基于二进制加权电容阵列的数字校准算法,并运用比较器自动失调校准技术,实现了高性能SARADC的设计。仿真结果表明该设计在120ksps的采样率下精度可达18位。

实现逐次逼近式ADC的方式千差万别,但其基本结构非常简单。如图1所示,模拟输入电压(VIN)由采样/保持电路保持。如图2所示,为实现二进制算法,N位寄存器首先设置在中间刻度(即:100…….00,MSB位1)。这样,数字模拟转换器(DAC)输出(VDAC)被设为VREF/2,VDAC是提供给ADC的基准电压。然后,比较判断VIN是小于还是大于VDAC.如果,VIN》VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1.相反,如果VIN《VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清为0.随后,逐次逼近控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。这个过程一直持续到最低有效位(LSB)。上述操作结束后就完成了转换,N位转换结果储存在寄存器内。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章