资料下载

ENC424J600/624j600独立10/100以太网控制器与SPI或并行接口数据表

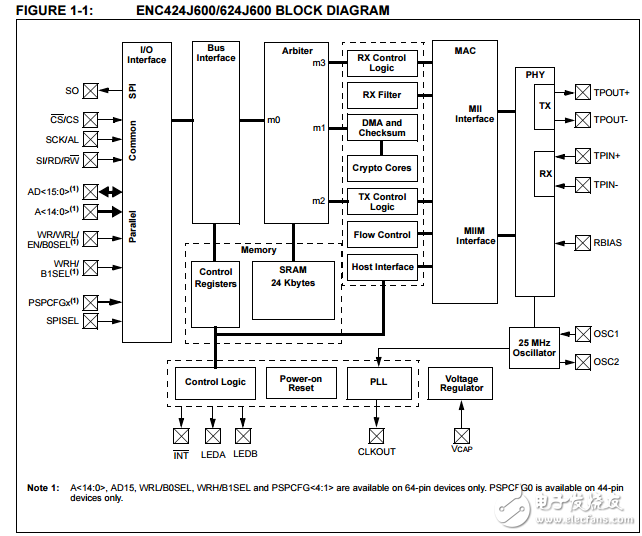

This document contains device-specific information for the following devices: • ENC424J600 • ENC624J600 The ENC424J600 and ENC624J600 are stand-alone, Fast Ethernet controllers with an industry standard Serial Peripheral Interface (SPI) or a flexible parallel interface. They are designed to serve as an Ethernet network interface for any microcontroller equipped with SPI or a standard parallel port. ENC424J600/624J600 devices meet all of the IEEE 802.3 specifications applicable to 10Base-T and 100Base-TX Ethernet, including many optional clauses, such as auto-negotiation. They incorporate a number of packet filtering schemes to limit incoming packets. They also provide an internal, 16-bit wide DMA for fast data throughput and support for hardware IP checksum calculations. For applications that require the security and authentication features of SSL, TLS and other protocols related to cryptography, a block of security engines is provided. The engines perform RSA, Diffie-Hellman, AES, MD5 and SHA-1 algorithm computations, allowing reduced code size, faster connection establishment and throughput, and reduced firmware development effort. Communication with the microcontroller is implemented via the SPI or parallel interface, with data rates ranging from 14 Mbit/s (SPI) to 160 Mbit/s (demultiplexed, 16-bit parallel interface)。 Dedicated pins are used for LED link and activity indication and for transmit/receive/DMA interrupts. A generous 24-Kbyte on-chip RAM buffer is available for TX and RX operations. It may also be used by the host microcontroller for general purpose storage. Communication protocols, such as TCP, can use this memory for saving data which may need to be retransmitted. For easy end product manufacturability, each ENC624J600 family device is preprogrammed with a unique nonvolatile MAC address. In most cases, this allows the end device to avoid a serialized programming step. The only functional difference between the ENC424J600 (44-pin) and ENC624J600 (64-pin) devices are the number of parallel interface options they support. These differences, along with a summary of their common features, are provided in Table 1-1. A general block diagram for the devices is shown in Figure 1-1. A list of the pin features, sorted by function, is presented in Table 1-2.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章