资料下载

基于CPLD控制的通用视频采集模块详述

本文实现了一种基于CPLD控制的视频采集模块。CPLD主要通过视频A/D的输出状态信号以及TMS320C6x DSP的相应输出控制信号生成FIFO的控制信号,实现视频数据流的传输通路。这种纯硬件实现的控制电路可以大大减少DSP的开销,减少软件实现的难度;同时可以作为一个集成的视频采集模块,用在一般的DSP芯片上,减少硬件开发的难度。

本文实现了一种在采集A/D模块、专用视频FIFO以及DSP微处理使用CPLD作为纯硬件控制的方案。使用这种方案的创新点是首先因为使用的是帧存储器FIFO,存储一帧或者一场视频数据,这样可以大大减轻DSP的开销,提高DSP的效率,从而更好的提高视频处理的实时性;其次因为接口逻辑比较复杂,一般用软件实现起来比较困难,使用可编程CPLD实现全部的硬件接口逻辑,减少软件设计的难度,减少DSP的开销。同时可以发挥CPLD现场可编程的特点,可以像软件一样更改;最后可以作为一个集成的通用硬件采集模块。

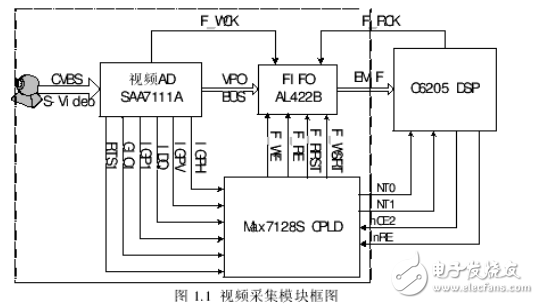

本文实现的是基于TI TMS320C6x的DSP的视频采集压缩卡的A/D采集模块以及接口控制模块。在采集模块主要功能是将从CCD摄像头输入的模拟视频信号转换为数字信号,普通CCD摄像头的输出是NTSC制式的复合全电视信号CVBS信号,通过SAA7114H TV解码芯片将模拟TV信号解码,转换为符合I TU R HT. 601标准的数字视频信号,并且由CPLD控制模块将数据存储到专用的视频FIFO芯片,中断DSP读取数据处理。具体的信号控制见图1.1。

2.模块介绍

2.1.视频采集模块

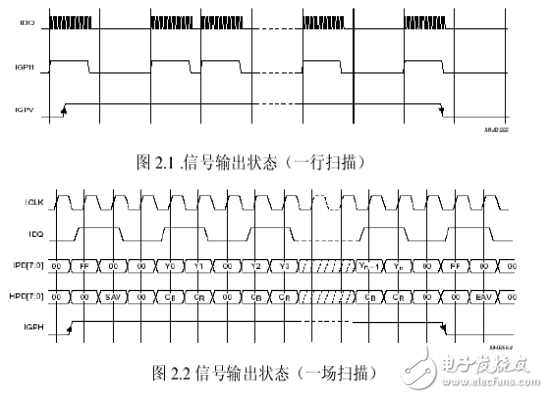

采集模块采用PHILIPS公司的视频A/D芯片SAA7114H,该专用视频A/D具有6路模拟视频输入,两个模拟预处理通道,并且抗混滤波、梳状滤波都被集成到芯片内部,这样对于硬件设计带来了极大的方便。同时场同步信号IGPV,行同步信号IGPH,有效图像数据输出信号IDQ,时车南毓中信昙rrr V都有管脚直接引出,这样省去了以往的时钟同步电路的设计,可靠性也有所提高。系统内部锁相环技术的集成使得可靠性和设计复杂度都有极大的降低。SAA7114H的配置支持IZC,可以通过DSP的通用I/O口软件模拟IZC总线。

从图2可以看出整个过程是在ICLK在上升沿触发,在IDQ有效的情况下传输的数据有效,数据输出的格式为(下为奇数场的一行数据扫描)

FF00 0080 UOYO, VOY1,UlY2, VlY3,。。.。。.。。……,U319Y638, V320Y639

其中FF00和0080是奇数场标志位。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章