资料下载

×

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

消耗积分:0 |

格式:rar |

大小:0.3 MB |

2017-10-27

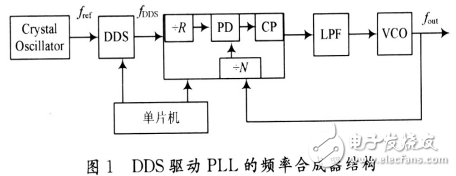

结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析和仿真,从仿真和测试结果看,该频率合成器达到了设计目标。该频率合成器的输出频率范围为 594~999 MHz,频率步进为5 Hz,相位噪声为-91dBc。

DDS的参考信号由晶振产生,其频率为fref。DDS输出的信号频率为fDDS,频率值由频率控制字(FTW)控制。锁相环(PLL)的参考信号由 DDS的输出信号驱动。VCO的输出频率由PLL芯片的电荷泵(CP)输出,并通过低通滤波器(LPF)后控制。频率合成器的输出信号为VCO的输出信 号。该频率合成器通过单片机提供控制信号,以改变DDS中FTW和PLL的分频比。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章