资料下载

×

基于FPGA的FIR数字滤波器设计方案解析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-10-29

实现数字化是控制系统的重要发展方向,而数字信号处理已在通信、语音、图像、自动控制、雷达、军事、航空航天等领域广泛应用。数字信号处理方法通常涉及变换、滤波、频谱分析、编码解码等处理。数字滤波是重要环节,它能满足滤波器对幅度和相位特性的严格要求,克服模拟滤波器所无法解决的电压和温度漂移以及噪声等问题。而有限冲激响应FIR滤波器在设计任意幅频特性的同时能够保证严格的线性相位特性。利用FPGA可以重复配置高精度的FIR滤波器,使用VHDL硬件描述语言改变滤波器的系数和阶数,并能实现大量的卷积运算算法。结合MATLAB工具软件的辅助设计,使得FIR滤波器具有快速、灵活、适用性强,硬件资源耗费少等特点。

2 基本原理

分布式算法(Distributed Arithmetic,简称DA)是一项重要的FPGA技术,广泛应用在计算乘积和之中。该算法基本原理如下:

一线性时不变网络输出:

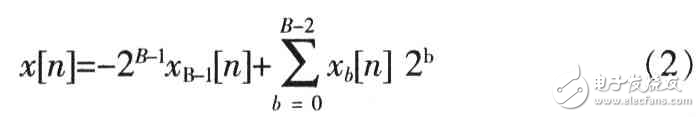

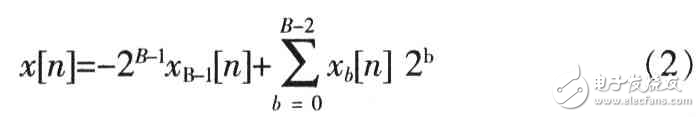

设系数c[n]是已知常数,x[n]是变量,在有符号DA系统中假设变量x[n]的表达式为:

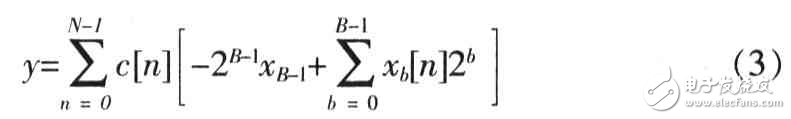

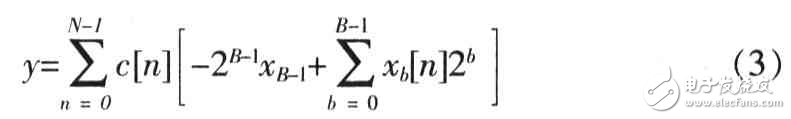

式中xb[n]为x[n]的第b位,而x[n]也就是x的第n次采样。于是,内积y可以表示为:

分布式算法是一种以实现乘加运算为目的的运算方法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序。该算法利用一个查找表(LUT)实现映射,即用一个2N字宽、预先编好程序的LUT接收一个N位输入向量xb=[xb[0]],xb[1],…,xb[N-1]]的映射,经查找表的查找后直接输出部分积。与传统算法相比,分布式算法可极大的减少硬件电路的规模,提高电路的执行速度。

2 基本原理

分布式算法(Distributed Arithmetic,简称DA)是一项重要的FPGA技术,广泛应用在计算乘积和之中。该算法基本原理如下:

一线性时不变网络输出:

设系数c[n]是已知常数,x[n]是变量,在有符号DA系统中假设变量x[n]的表达式为:

式中xb[n]为x[n]的第b位,而x[n]也就是x的第n次采样。于是,内积y可以表示为:

分布式算法是一种以实现乘加运算为目的的运算方法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序。该算法利用一个查找表(LUT)实现映射,即用一个2N字宽、预先编好程序的LUT接收一个N位输入向量xb=[xb[0]],xb[1],…,xb[N-1]]的映射,经查找表的查找后直接输出部分积。与传统算法相比,分布式算法可极大的减少硬件电路的规模,提高电路的执行速度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章