资料下载

×

在DSP基础上实现数字图像的混沌加密及硬件实现方法

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-10-30

介绍了在DSP基础上,实现数字图像的混沌加密及硬件实现方法。根据离散化和数字化处理技术,对三维Lorenz混沌系统作离散化处理,用C语言和DSP技术产生三维Lorenz混沌迭代序列,分别对数字图像的红、绿、蓝三基色信号进行混沌加密和解密。基于芯片型号为TMS32 0VC5509A的DSP开发平台,以bmp格式的灰度图像为例,设计了Lorenz混沌序列对数字图像进行加密与解密算法,给出了DSP硬件实现结果表明,改善了安全性、提高了速度、满足了实时性要求。

关键词: Lorenz系统;图像加密;DSP;混沌加密;硬件实现

随着计算机及通信技术的发展,图像处理及应用愈加广泛。现代DSP技术的发展和应用为实现图像处理奠定了基础。高性能的DSP处理器作为图像处理首选的核心器件,并能通过软件编程实现各种处理算法,提高系统处理能力和扩展系统功能。

近来混沌的同步控制理论日趋成熟,为混沌在通信中的应用提供了理论基础。混沌信号的非周期性连续宽带频谱,类似噪声的特性。另外,混沌信号对初始条件的高度敏感,即使两个完全相同的混沌系统从近乎相同的初始条件开始演化,其轨道将很快变得互不相关,这使得混沌信号具有长期不可预测性和抗截获能力。而且具有多个正李氏指数的超混沌系统,及复杂的运动轨迹,这使得混沌信号具有较高的复杂度。同时混沌系统本身具有确定性,由非线性系统的方程、参数和初始条件所决定,因此,混沌信号易于产生复制。混沌信号的隐蔽性、不可预测性、高复杂度和易于实现等特性都适合于保密通信。与其他加密方法不同的是,混沌加密是一种动态加密方法,由于其处理速度和密钥长度无关,因此这种方法的计算效率高、可用于实时信号处理和静态加密场合。且用此方法加密的信息很难破译,具有很高的保密度。即使在连续摄动存在的情况下,混沌同步效应过程也是稳定的。特别是在混沌信号上加上一个较小的信息源,当混合信号传到接收器上后,由接收器上参数相同的混沌电路捕捉其中主要的混沌分量,可以较好地恢复输送的信息源。

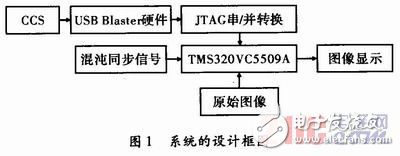

目前对混沌加密的实现还局限于计算机仿真,有关硬件实现的报道也很少。而用于混沌加密的系统,通常是一维或二维,如Logistic映射等,这类系统的方程形式简单且易于实现,但存在密钥空间小、抵御穷举攻击能力差、容易被相空间重构方法进行混沌系统识别等问题。针对上述问题本文提出了用三维Lorenz混沌系统和DSP技术实现混沌数字图像加密及其硬件实现的新方法。根据离散化和数字化处理技术,对三维Lorenz系统作离散化处理后,能产生混沌迭代序列。在设计图像红、绿、蓝三基色信号混沌加密与解密算法的基础上,利用芯片型号为TMS320VC5509A的DSP开发平台,进行了8×8的bmp格式灰度图像加密与解密的硬件实验研究,并给出了实验结果,其系统框图如图1所示。

1 Lorenz系统离散化及DSP硬件实现

Lorenz系统作为经典三维混沌系统,生成的混沌序列有其自身的特点。与一维和二维等低维混沌系统相比,具有更为复杂的混沌动力学行为,产生的混沌序列更不可预测。系统的3个初始值和3个参数都可以作为生成加密混沌序列的种子密钥,产生的密钥空间大于一维和二维的混沌系统。如果对系统输出的混沌序列进行处理,还可以采用单变量或多变量组合的加密混沌序列,使得序列密码的设计和应用更加灵活方便。

由于Lorenz系统是三维连续混沌系统,而DSP只能处理数字信号或离散信号,所以要先对连续混沌系统作离散化处理。对混沌系统离散化通常有3种方法。Euler算法、改进Euler算法和Runge—Kutta算法。这3种离散化的方法各有优缺点,一些较简单的一维和二维混沌系统,常使用精度较高的Runge—Kutta算法,由于受到硬件资源的限制,一般用Euler算法在型号为TMS320VC5509A的DSP平台上产生Lorenz混沌序列。

在选择存储器时应从以下方面考虑:首先图像压缩算法中间数据量大,要求处理器的片上内存尽可能大,尽量避免对外部存储器读写操作。TMS320VC5509A的片上存储器包括32 k位×16位DARAM,96 k位×16位SARAM,共128 k位的存储空间。其中DARAM为双地址,在每个周期内可以对其进行2次操作(2次读,2次写,1次读和1次写),这样增加片上存储器的利用率。其次,VC5509A片上资源丰富,包括I2C总线,3个Mc-BSPs。VC5509A采用144引脚LQFP封装,便于安装、调试;VC5509A功耗小,工作在200 MHz主频下,功耗仅100 mW,适合嵌入式应用。

DSP基本系统由独立的电源系统供电,而硬件平台的其他器件共用另一套电源供电系统。为了降低系统功耗,DSP一般采用低电压供电,并且采用I/O和CPU内核分开供电方式。TMS320VC5509A不同的工作频率要求不同的核电压,200 MHz为1.6 V,144 MHz为1.35V,108 MHz为1.2 V。DSP的I/O电压为3.3 V。

高速DSP芯片主要特性如下:

(1)低功耗设计,比上一代C54XX器件功耗低约30%。处理速度快,双核结构,处理速度400MI·s-1。采用超长指令结构(VLIW),单指令字长32位。外部时钟40 MHz,内部时钟20 MHz,所有指令均单周期完成,处理器内部采用高度并行机制,可同时进行多达11项各类操作。

(2)两套相同的外部数据、地址总线,支持局部存储器和全局共享存储器。

(3)6个高速并行通信口,采用异步传输方式,最大速率可达20 Mb·s-1。通过令牌传递可灵活实现数据双向传输,这种结构适合DM642之间的互连。

(4)6个DMA通道,每个通道的最大速率可达20 Mb·s-1。DMA内部总线与CPU的地址、数据、指令总线完全分开,避开了总线使用上的瓶颈。

综上所述,在选用DSP芯片时,应考虑性能是否满足快速判读算法的要求,即选择那些指令周期短、数据吞吐率高、通信能力强、指令集功能完备的处理器,同时还要兼顾功耗和开发支持环境等因素。本设计采用TI公司的TMS320VC5509A芯片,选择TMS320VC5509A作为主处理器芯片。

关键词: Lorenz系统;图像加密;DSP;混沌加密;硬件实现

随着计算机及通信技术的发展,图像处理及应用愈加广泛。现代DSP技术的发展和应用为实现图像处理奠定了基础。高性能的DSP处理器作为图像处理首选的核心器件,并能通过软件编程实现各种处理算法,提高系统处理能力和扩展系统功能。

近来混沌的同步控制理论日趋成熟,为混沌在通信中的应用提供了理论基础。混沌信号的非周期性连续宽带频谱,类似噪声的特性。另外,混沌信号对初始条件的高度敏感,即使两个完全相同的混沌系统从近乎相同的初始条件开始演化,其轨道将很快变得互不相关,这使得混沌信号具有长期不可预测性和抗截获能力。而且具有多个正李氏指数的超混沌系统,及复杂的运动轨迹,这使得混沌信号具有较高的复杂度。同时混沌系统本身具有确定性,由非线性系统的方程、参数和初始条件所决定,因此,混沌信号易于产生复制。混沌信号的隐蔽性、不可预测性、高复杂度和易于实现等特性都适合于保密通信。与其他加密方法不同的是,混沌加密是一种动态加密方法,由于其处理速度和密钥长度无关,因此这种方法的计算效率高、可用于实时信号处理和静态加密场合。且用此方法加密的信息很难破译,具有很高的保密度。即使在连续摄动存在的情况下,混沌同步效应过程也是稳定的。特别是在混沌信号上加上一个较小的信息源,当混合信号传到接收器上后,由接收器上参数相同的混沌电路捕捉其中主要的混沌分量,可以较好地恢复输送的信息源。

目前对混沌加密的实现还局限于计算机仿真,有关硬件实现的报道也很少。而用于混沌加密的系统,通常是一维或二维,如Logistic映射等,这类系统的方程形式简单且易于实现,但存在密钥空间小、抵御穷举攻击能力差、容易被相空间重构方法进行混沌系统识别等问题。针对上述问题本文提出了用三维Lorenz混沌系统和DSP技术实现混沌数字图像加密及其硬件实现的新方法。根据离散化和数字化处理技术,对三维Lorenz系统作离散化处理后,能产生混沌迭代序列。在设计图像红、绿、蓝三基色信号混沌加密与解密算法的基础上,利用芯片型号为TMS320VC5509A的DSP开发平台,进行了8×8的bmp格式灰度图像加密与解密的硬件实验研究,并给出了实验结果,其系统框图如图1所示。

1 Lorenz系统离散化及DSP硬件实现

Lorenz系统作为经典三维混沌系统,生成的混沌序列有其自身的特点。与一维和二维等低维混沌系统相比,具有更为复杂的混沌动力学行为,产生的混沌序列更不可预测。系统的3个初始值和3个参数都可以作为生成加密混沌序列的种子密钥,产生的密钥空间大于一维和二维的混沌系统。如果对系统输出的混沌序列进行处理,还可以采用单变量或多变量组合的加密混沌序列,使得序列密码的设计和应用更加灵活方便。

由于Lorenz系统是三维连续混沌系统,而DSP只能处理数字信号或离散信号,所以要先对连续混沌系统作离散化处理。对混沌系统离散化通常有3种方法。Euler算法、改进Euler算法和Runge—Kutta算法。这3种离散化的方法各有优缺点,一些较简单的一维和二维混沌系统,常使用精度较高的Runge—Kutta算法,由于受到硬件资源的限制,一般用Euler算法在型号为TMS320VC5509A的DSP平台上产生Lorenz混沌序列。

在选择存储器时应从以下方面考虑:首先图像压缩算法中间数据量大,要求处理器的片上内存尽可能大,尽量避免对外部存储器读写操作。TMS320VC5509A的片上存储器包括32 k位×16位DARAM,96 k位×16位SARAM,共128 k位的存储空间。其中DARAM为双地址,在每个周期内可以对其进行2次操作(2次读,2次写,1次读和1次写),这样增加片上存储器的利用率。其次,VC5509A片上资源丰富,包括I2C总线,3个Mc-BSPs。VC5509A采用144引脚LQFP封装,便于安装、调试;VC5509A功耗小,工作在200 MHz主频下,功耗仅100 mW,适合嵌入式应用。

DSP基本系统由独立的电源系统供电,而硬件平台的其他器件共用另一套电源供电系统。为了降低系统功耗,DSP一般采用低电压供电,并且采用I/O和CPU内核分开供电方式。TMS320VC5509A不同的工作频率要求不同的核电压,200 MHz为1.6 V,144 MHz为1.35V,108 MHz为1.2 V。DSP的I/O电压为3.3 V。

高速DSP芯片主要特性如下:

(1)低功耗设计,比上一代C54XX器件功耗低约30%。处理速度快,双核结构,处理速度400MI·s-1。采用超长指令结构(VLIW),单指令字长32位。外部时钟40 MHz,内部时钟20 MHz,所有指令均单周期完成,处理器内部采用高度并行机制,可同时进行多达11项各类操作。

(2)两套相同的外部数据、地址总线,支持局部存储器和全局共享存储器。

(3)6个高速并行通信口,采用异步传输方式,最大速率可达20 Mb·s-1。通过令牌传递可灵活实现数据双向传输,这种结构适合DM642之间的互连。

(4)6个DMA通道,每个通道的最大速率可达20 Mb·s-1。DMA内部总线与CPU的地址、数据、指令总线完全分开,避开了总线使用上的瓶颈。

综上所述,在选用DSP芯片时,应考虑性能是否满足快速判读算法的要求,即选择那些指令周期短、数据吞吐率高、通信能力强、指令集功能完备的处理器,同时还要兼顾功耗和开发支持环境等因素。本设计采用TI公司的TMS320VC5509A芯片,选择TMS320VC5509A作为主处理器芯片。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章