资料下载

SST39VF401C/402C/SST39LF401C/402C中文资料数据手册PDF免费下载(闪存技术)

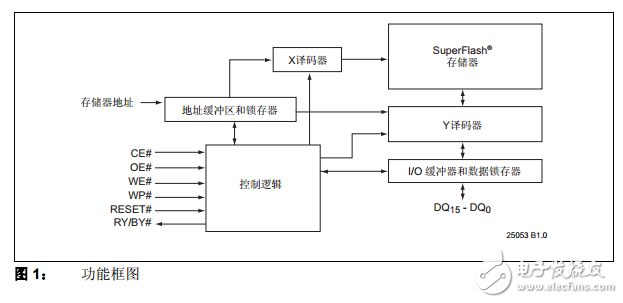

SST39VF401C/402C 和 SST39LF401C/402C 是采用 SST 专有的高性能 CMOS SuperFlash® 技术制造的 512K x16 CMOS 多用途闪存 + (MPF+)器件。与其他方法相比,分离栅极单元设计和厚氧化层隧穿注入器可实现更高的可靠性和可制造性。SST39VF401C/402C 和 SST39LF401C/402C 使用 2.7-3.6V 电源进行写操作 (编程或擦除)。这些器件遵从 x16 存储器的 JEDEC 标准引脚排列。 SST39VF401C/402C和SST39LF401C/402C器件具有高性能的字编程能力,其典型字编程时间为7 µs。这些器件使用翻转位、数据 # 查询或 RY/BY# 引脚来指示编程操作是否完成。为了防止意外写操作,这些器件提供了片上硬件和软件数据保护方案。这些器件针对一系列广泛应用进行设计、制造和测试,典型可擦写次数可确保达到 100,000 次。数据额定保存时间则大于 100 年。 SST39VF401C/402C 和 SST39LF401C/402C 器件适用于需要方便且经济地更新程序、配置或数据存储器的应用。对于所有系统应用,它们都可以显著提高性能和可靠性,同时降低功耗。相较于其他闪存技术,它们本质上在擦除和编程期间消耗的能量更低。消耗的总能量是应用中施加电压、电流和时间的函数。对于任何给定的电压范围,SuperFlash 技术的编程电流更低、擦除时间更短;因此,在任何擦除或编程操作期间消耗的总能量低于其他闪存技术。在降低程序、数据和配置存储应用成本的同时,这些器件还可以提高灵活性。 SuperFlash 技术支持固定的擦除和编程时间,时间与所发生的擦除 / 编程次数无关。因此,系统软件或硬件不需要进行修改或降额,这一点不同于其他一些擦除和编程时间会随擦除 / 编程次数累积而增加的闪存技术。为了满足高密度、表面贴装的要求,SST39VF401C/402C 和 SST39LF401C/402C 提供了 48 引脚 TSOP、 48 球 TFBGA 和 48 球 WFBGA 封装。关于引脚分配,请参见图 2、图 3 和图 4。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章