资料下载

×

基于DSP平台的快速H.264编码算法的设计解析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-04

视频压缩编码标准H.264/AVC是由ISO/IEC和ITU-T组成的联合视频专家组(JVT)制定的,他引进了一系列先进的视频编码技术,如4×4整数变换、空域内的帧内预测,多参考帧与多种大小块的帧间预测技术等,标准一经推出,就以其高效的压缩性能和友好的网络特性受到业界的广泛推崇。特别是在2004年7月JVT组织做了重要的保真度范围扩展的补充后,更加扩大了标准的应用范围,但同时巨大的运算量却成为其广泛应用的瓶颈。考虑到H.264协议实现的复杂度,本文的思路是:一方面提高硬件处理速度和能力,采用TI公司最新的数字媒体处理器Davinci TMS320DM6446 DSP芯片作为H.264编码器实现的硬件开发平台,另一方面提高算法效率。最后提出一个基于这个芯片的嵌入式H.264编码器的设计方案。

1 硬件平台

1.1 Davinci DM6446芯片介绍

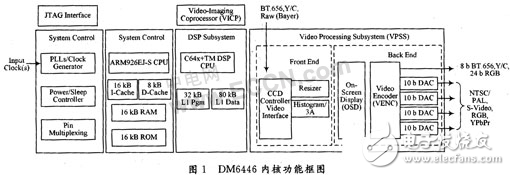

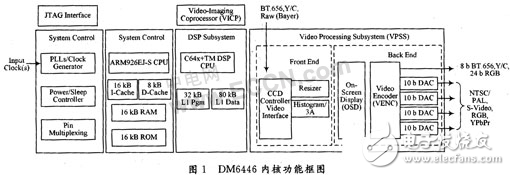

DM6446采用DSP+ARM的双内核结构(内核图见图1),其中的DSP芯片的CPU时钟频率可达594 MHz,ARM的引入可以释放DSP在控制方面的部分功能,使DSP专门进行数据处理的工作。芯片采用增强型的哈佛结构总线,其CPU内部有2个数据通道,8个32 b的功能单元,2个通用寄存器组(A和B),可同时执行8条32 b长指令。如果能充分利用这8个功能单元,总字长为256 b的指令包同时分配到8个并行处理单元,在完全流水的情况下,该芯片的指令吞吐量将达到594×8=4 752 MIPS。处理器具有双16 b扩充功能,芯片能在一个周期内完成双16 b的乘法、加减法、比较、移位等操作。该芯片内部支持两级Cache,其中第一级32 kB的程序缓存器L1P,80 kB的数据缓存器L1D,而第二级的Cache大小是可配置的64 kB,芯片自动完成这两级Cache之间数据一致性的维护。有了这两级Cache的支持将使CPU的执行速度大大加快。

Davinci DM6446具有专用的视频图像处理子系统。视频处理子系统包括1个视频前端和1个视频末端,视频前端的输入接口用于接受外部传感器或视频译码器输出的BT.656等图像输入信息;视频末端输出接口输出图像,实现图像本地重现。

视频前端输入(VPFE)接口由1个CCD控制器(CCDC),1个预处理器,柱状模块,自动曝光/白平衡/聚焦模块(H3A)和寄存器组成。CCD控制器可以与视频解码器CMOS传感器或电荷耦合装置连接。预处理器是一个实时的图形处理器。

1.2 H.264编码器硬件平台

本系统的平台核心处理芯片为Davinci DM6446,如图2所示,片外RAM选取两片DDR并联成32位的数据宽度,空间为256 MB。模拟视频信号在“VIDEO IN”引入后经过解码芯片TVP5146变换为数字信号后输入TMS320DM6446芯片中进行处理,H.264编码处理后的码流可以通过视频末端输出保存在本地硬盘上,以方便调试检查。或者可以通过10/100 M以太网物理层接口输出,进行网络传输。同时,本地的重构图像可以通过TMS320DM6446芯片内部OSD模块和编码模块D/A变换后直接显示输出。

1 硬件平台

1.1 Davinci DM6446芯片介绍

DM6446采用DSP+ARM的双内核结构(内核图见图1),其中的DSP芯片的CPU时钟频率可达594 MHz,ARM的引入可以释放DSP在控制方面的部分功能,使DSP专门进行数据处理的工作。芯片采用增强型的哈佛结构总线,其CPU内部有2个数据通道,8个32 b的功能单元,2个通用寄存器组(A和B),可同时执行8条32 b长指令。如果能充分利用这8个功能单元,总字长为256 b的指令包同时分配到8个并行处理单元,在完全流水的情况下,该芯片的指令吞吐量将达到594×8=4 752 MIPS。处理器具有双16 b扩充功能,芯片能在一个周期内完成双16 b的乘法、加减法、比较、移位等操作。该芯片内部支持两级Cache,其中第一级32 kB的程序缓存器L1P,80 kB的数据缓存器L1D,而第二级的Cache大小是可配置的64 kB,芯片自动完成这两级Cache之间数据一致性的维护。有了这两级Cache的支持将使CPU的执行速度大大加快。

Davinci DM6446具有专用的视频图像处理子系统。视频处理子系统包括1个视频前端和1个视频末端,视频前端的输入接口用于接受外部传感器或视频译码器输出的BT.656等图像输入信息;视频末端输出接口输出图像,实现图像本地重现。

视频前端输入(VPFE)接口由1个CCD控制器(CCDC),1个预处理器,柱状模块,自动曝光/白平衡/聚焦模块(H3A)和寄存器组成。CCD控制器可以与视频解码器CMOS传感器或电荷耦合装置连接。预处理器是一个实时的图形处理器。

1.2 H.264编码器硬件平台

本系统的平台核心处理芯片为Davinci DM6446,如图2所示,片外RAM选取两片DDR并联成32位的数据宽度,空间为256 MB。模拟视频信号在“VIDEO IN”引入后经过解码芯片TVP5146变换为数字信号后输入TMS320DM6446芯片中进行处理,H.264编码处理后的码流可以通过视频末端输出保存在本地硬盘上,以方便调试检查。或者可以通过10/100 M以太网物理层接口输出,进行网络传输。同时,本地的重构图像可以通过TMS320DM6446芯片内部OSD模块和编码模块D/A变换后直接显示输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章