资料下载

×

汽车音响导航系统高速DDR200 PCB的信号完整性设计分析

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-11-27

在以往汽车音响的系统设计当中, 一块PCB上的最高时钟频率在30~50MHz已经算是很高了,而现在多数PCB的时钟频率超过100MHz,有的甚至达到了GHz数量级。为此,传统的以网表驱动的串行式设计方法已经不能满足今天的设计要求,现在必须采用更新的设计理念和设计方法,即将以网表驱动的串行的设计过程, 改变成将整个设计各环节并行考虑的一个并行过程。也就是说将以往只在PCB布局、布线阶段才考虑的设计要求和约束条件, 改在原理图设计阶段就给予足够的关注和评估,在设计初期就开始分析关键器件的选择,构想关键网线的拓扑结构,端接匹配网络的设定, 以及在布线开始前就充分考虑PCB的叠层结构,减免信号间的串扰方法,保证电源完整性和时序等因素。

本文主要介绍在汽车音响导航系统中使用的高速DDR200,在兼顾高速电路的基本理论和专业化设计经验的指导下, 保证信号完整性的PCB设计方法。

1 什么是DDR 及其基本工作原理

DDR SDRAM, 习惯称为DDR.DDR SDRAM即双倍速率同步动态随机存储器。

DDR内存是在SDRAM 内存基础上发展而来的。SDRAM在一个时钟周期内只传输一次数据, 它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据, 它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到双倍的数据传输率。

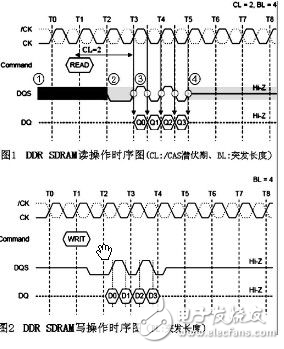

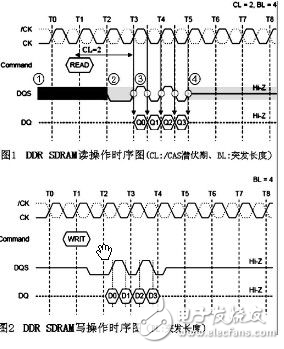

如下图1和图2所示,DDR SDRAM相对SDRAM多了两个信号: CLK# 与DQS。

CLK# 与正常CLK时钟相位相反, 形成差分时钟信号。而数据的传输在CLK与CLK# 的交叉点进行, 即在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现双倍速率传输。

DQS(DQ STrobe、数据选取脉冲)是DDRSDRAM中的重要功能, 主要用来在一个时钟周期内准确的区分出每个传输周期,并在接收端使用DQS来读出相应的数据DQ。

DQS在上升沿和下降沿都有效,与数据信号同时生成。DQS和DQ都是三态信号双向传输。在读操作时,DQS信号的边沿在时序上与DQ 的信号边沿处对齐, 而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐。

本文主要介绍在汽车音响导航系统中使用的高速DDR200,在兼顾高速电路的基本理论和专业化设计经验的指导下, 保证信号完整性的PCB设计方法。

1 什么是DDR 及其基本工作原理

DDR SDRAM, 习惯称为DDR.DDR SDRAM即双倍速率同步动态随机存储器。

DDR内存是在SDRAM 内存基础上发展而来的。SDRAM在一个时钟周期内只传输一次数据, 它是在时钟的上升期进行数据传输;而DDR内存则是一个时钟周期内传输两次数据, 它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR内存可以在与SDRAM相同的总线频率下达到双倍的数据传输率。

如下图1和图2所示,DDR SDRAM相对SDRAM多了两个信号: CLK# 与DQS。

CLK# 与正常CLK时钟相位相反, 形成差分时钟信号。而数据的传输在CLK与CLK# 的交叉点进行, 即在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现双倍速率传输。

DQS(DQ STrobe、数据选取脉冲)是DDRSDRAM中的重要功能, 主要用来在一个时钟周期内准确的区分出每个传输周期,并在接收端使用DQS来读出相应的数据DQ。

DQS在上升沿和下降沿都有效,与数据信号同时生成。DQS和DQ都是三态信号双向传输。在读操作时,DQS信号的边沿在时序上与DQ 的信号边沿处对齐, 而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章