资料下载

×

LUCT工具主要特性及不确定性时钟树设计方法和算法的介绍

消耗积分:0 |

格式:rar |

大小:1.2 MB |

2017-11-29

时钟树设计及其设计方式是引起系统芯片性能差异的主要原因。

低不确定性时钟树[LUCT]设计及算法与在系统芯片上实现的第一层时钟树的物理定义有关,能够让设计人员克服传统设计方法的所有低效率问题。

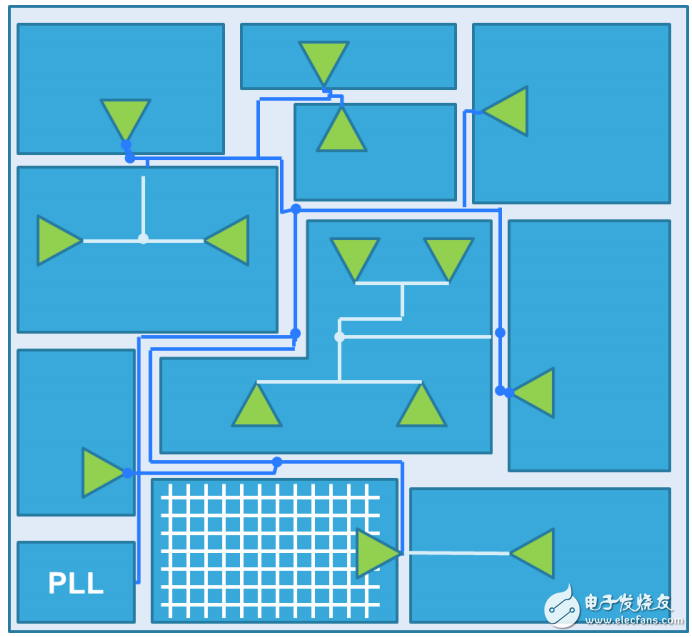

从顶层的根时钟网络(通常是 PLL 输出)到中层时钟网络,LUCT 是一个高质量的负载均衡的时钟树,其目标是将时钟信号从中央锁相环 PLL 送到芯片的大部分区域,详情参见参考文献。该文献详细介绍了低不确定性时钟树[LUCT]方法和架构,概括了从规格定义到单元布局和时钟合成的全部相关设计流程。

图 1:在 ASIC 设计中优化时钟分配

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章