资料下载

×

一种新颖的图像缩放算法进行FPGA硬件实现

消耗积分:1 |

格式:rar |

大小:0.65 MB |

2017-12-12

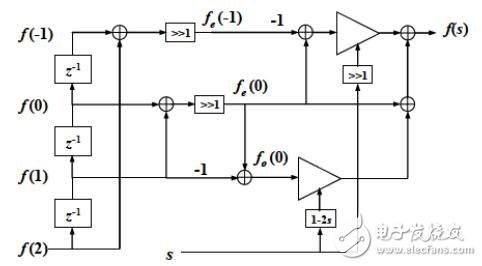

本文选择了一种新颖的图像缩放算法进行FPGA硬件实现。该算法基于奇偶分解的思想,具有复杂度低、硬件需求小和缩放效果良好等突出优点。首先利用MATLAB对该算法进行了功能验证,然后用缩放耗时、PSNR、边缘模糊等级和脉冲噪声等指标评估基于该算法图像处理效果。与传统时域算法作对比,对比结果表明该算法在处理效果和运算速度上的优异性。基于Zedboard开发板,运用Vivado HLS高级综合工具将算法的C程序综合成硬件IP,并搭建了包含ARM处理器和VGA等模块的软硬协同验证系统。实验验证了图像缩放算法硬件设计的正确性和实用性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章