资料下载

×

高速数字接口拓扑结构设计

消耗积分:1 |

格式:rar |

大小:0.46 MB |

2017-12-26

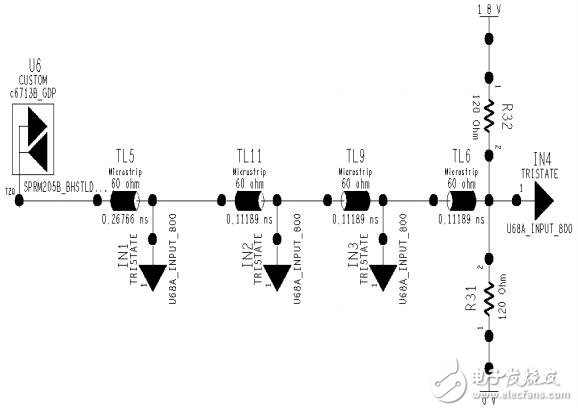

信号完整性(SI)是在高速产品中由互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能。其实简单的理解就是只要是影响了信号质量或时序的问题,就可归结为信号完整性问题。随着信号频率的不断提高,高速互连线之间的拓扑电路的设计方法也在发生变化,当下一般对这类拓扑的设计,大都采用一些既定的方案或经验法则,往往在制板调试阶段才能发现信号的传输出现问题,这样重新再板既费时费力,又增加了成本,本文基于SI的仿真设计就是在电路设计的同时已经考虑到了SI的风险,并使用仿真工具来量化信号的各项性能指标,指定详细的SI设计规则,使设计的电路最大可能的降低风险。

国外的科技巨头早就意识到了这个问题,并拥有自己专属的信号完整性(SI)工程师,他们与电路设计师以及PCB设计师一起相互协作,共同解决在产品研发过程中所出现的信号完整性问题。根据尚普咨询给出相关数据显示,过去十年来,全球PCB持续向亚洲尤其是中国大陆迁移,中国大陆迅速成为电子产品和PCB生产大国,并且在未来几年内将继续保持快速增长,这种快速增长也必将促使国内各研究机构和公司在信号完整性理论基础、设计沆程、工程实践中加大投入资金和人力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章