资料下载

×

Verilog和VHDL的状态机设计技术的详细资料免费下载

消耗积分:0 |

格式:pdf |

大小:0.14 MB |

2018-09-23

设计同步有限状态机(FSM)是数字逻辑工程师的共同任务。本文将讨论SimopySesign CPLILRIL1关于FSM设计的各种问题。Verilog和VHDL编码风格将被呈现。将使用真实世界的例子来比较不同的方法。

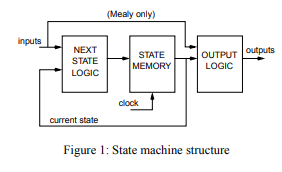

有限状态机2具有图1所示的一般结构。

机器的当前状态被存储在状态存储器中,一组n个触发器由单个时钟信号(因此“同步”状态机)计时。状态向量(也是当前状态,或者只是状态)是当前状态存储器存储的值。机器的下一个状态是状态向量和输入的函数。膳食输出_7_是状态向量和输入的函数,而摩尔输出_8_仅是状态向量的函数。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

春花秋月真

2019-03-17

0 回复 举报赞一个! 收起回复

春花秋月真

2019-03-17

0 回复 举报赞一个! 收起回复

- 相关下载

- 相关文章