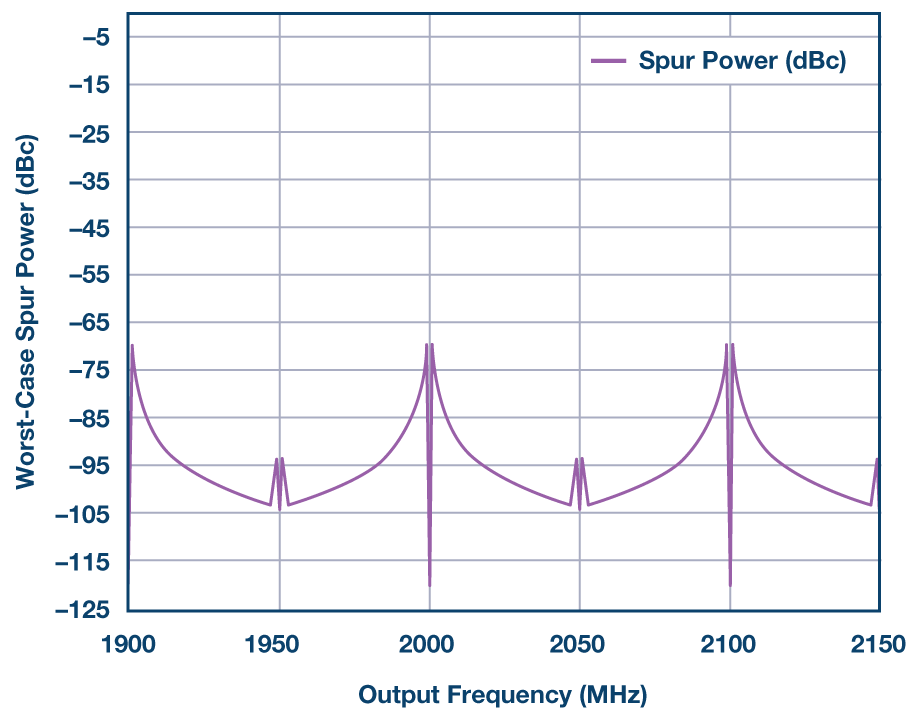

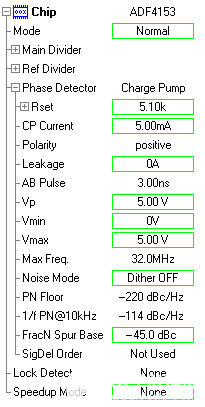

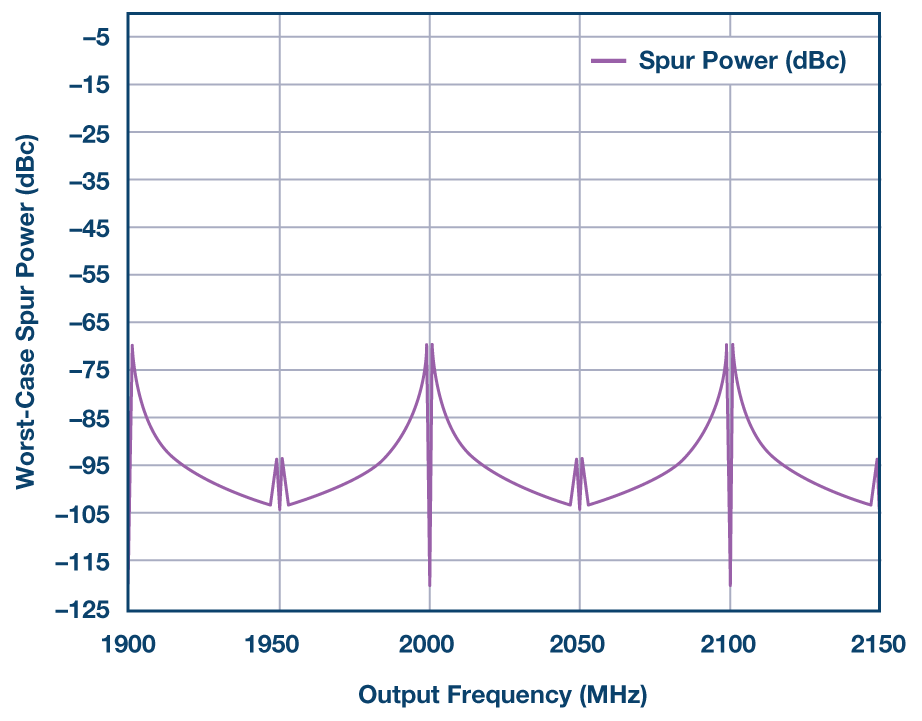

分析优化和消除具有高达13.6GHz VCO的锁相环中的整数边界杂散

如何设计和调试锁相环电路

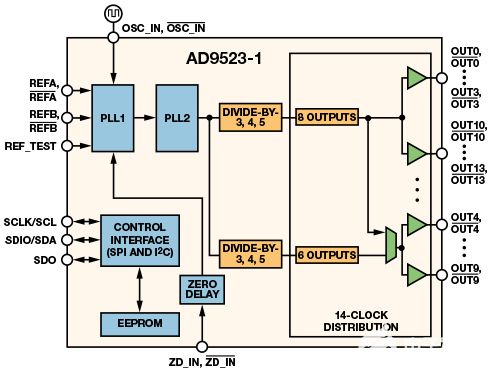

双环路时钟发生器清除抖动提供多个高频输出

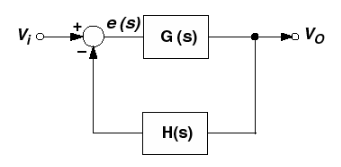

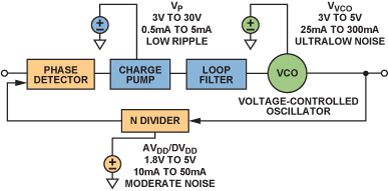

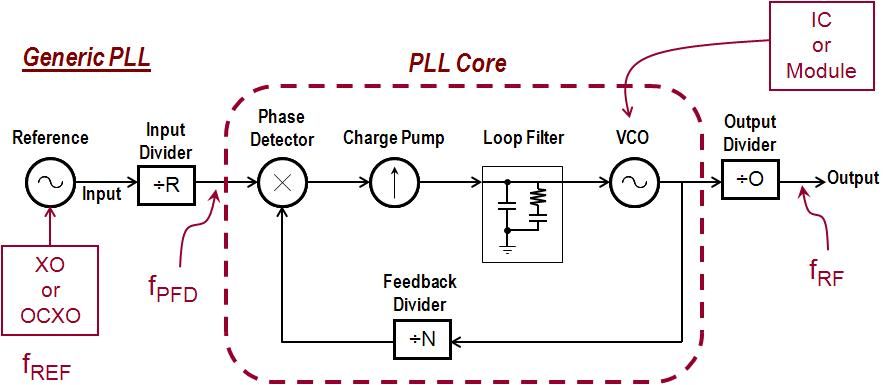

构成PLL频率合成器的构建模块研究

PLL的相位噪声和参考杂散参数在开环调制方案中的重要性

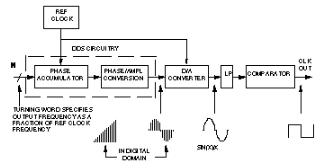

单芯片直接数字频率合成与模拟PLL的比较

使用ADF4111频率合成器和VCO190-902T压控振荡器的实用PLL电路

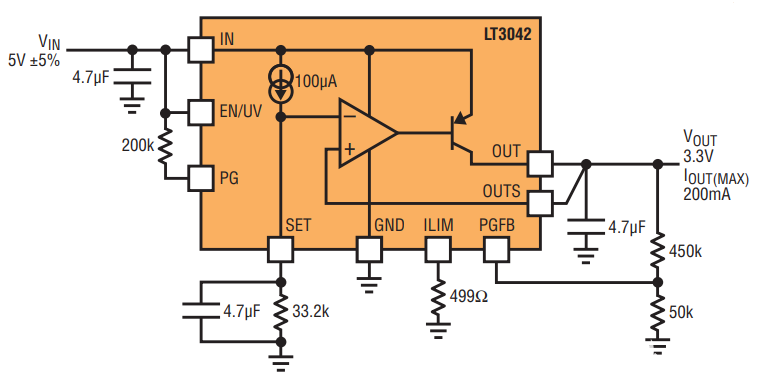

锁相环的电源管理设计

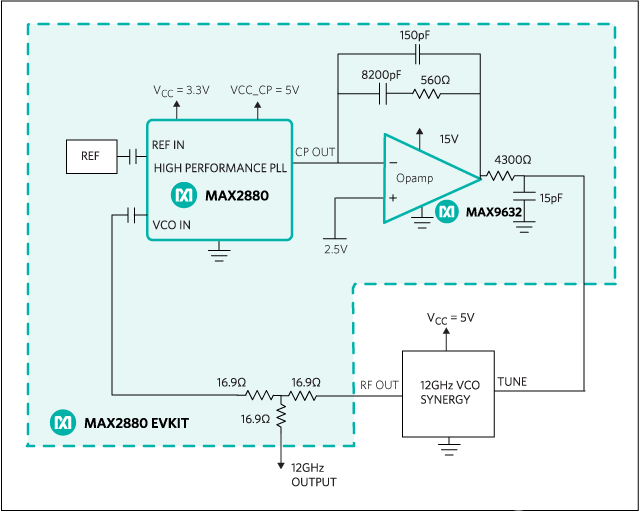

12GHz、超低相位噪声小数N分频锁相环的设计

利用硅双极宽带PLL构建模块集成电路

整数N分频和小数N分频PLL频率合成器的相位噪声

LT3042高性能低压差线性稳压器用于为噪声敏感型供电应用

分析优化和消除具有高达13.6 GHz VCO的锁相环中的整数边界杂散

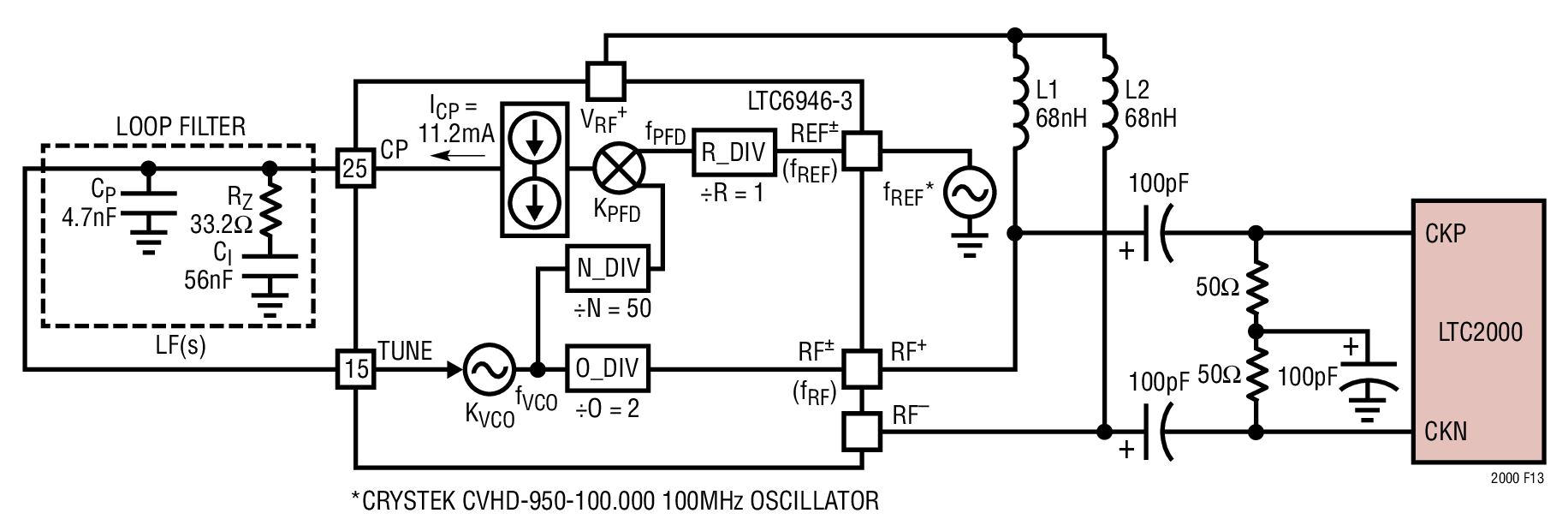

适用于16位2.5Gsps高性能DAC的不折不扣的时钟解决方案

分析和管理电源噪声和时钟抖动对高速DAC相位噪声的影响

ADF4356/ADF5356器件上的相位对齐和控制

时钟失效之后,STM32还能运行?

FPGA知识汇集-FPGA系统时序理论

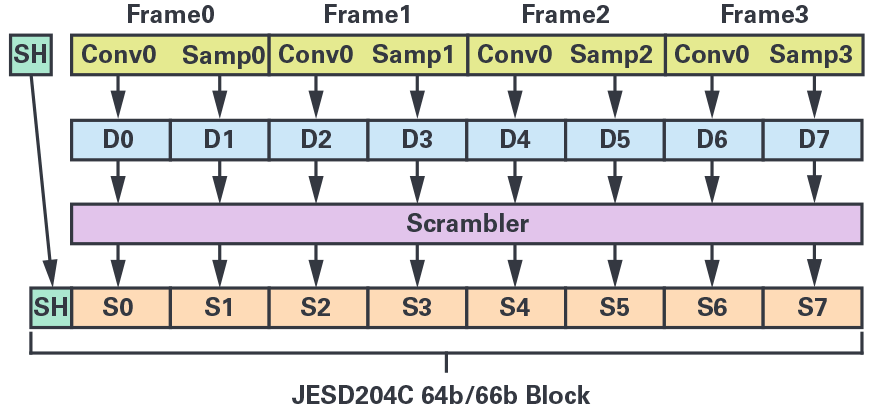

JESD204C入门:新增功能应用

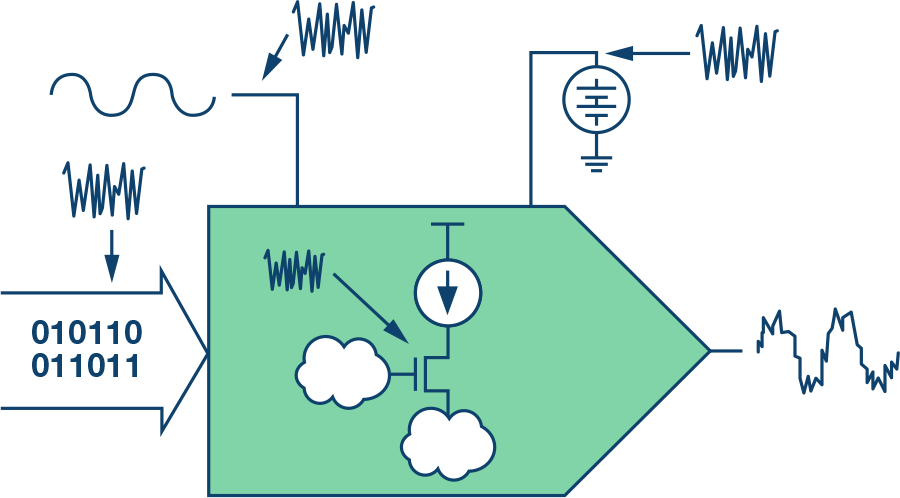

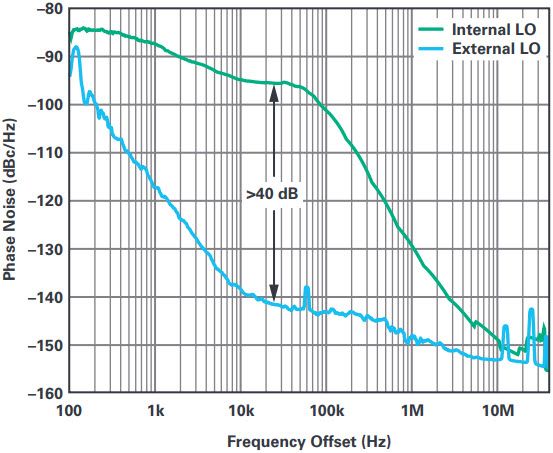

收发器相位噪声拆解通过外部LO提供性能