资料下载

Cyclone V FPGA系列中文学习教程免费下载

本章节介绍了Cyclone ® V核心架构中逻辑阵列模块(LAB)的功能特性。

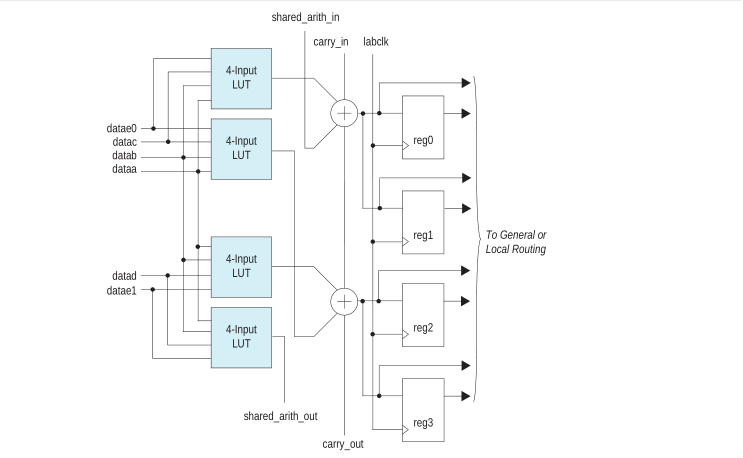

LAB是由称作自适应逻辑模块(ALM)的基本构造模块组成,通过配置这些模块能够实现逻辑功能、算术功能以及寄存器功能。

您可以将Cyclone V器件中1/4的LAB用作存储器LAB (MLAB)。

Quartus ® II软件和所支持的第三方综合工具,与参数化功能(例如参数化模块库(LPM))一起,对常用功能(例如:计数器、加法器、减法器和算术功能) 自动选择相应的模式。

本章节涵盖以下两方面内容:

• LAB

• ALM操作模式

LAB是由一组逻辑资源组成的可配置逻辑模块。每个LAB均包含专用逻辑,用来将控制信号驱动到ALM中。

MLAB是LAB的超集,包含了LAB的所有特性。

LAB控制信号

每个LAB均包含专用逻辑,将控制信号驱动到它的ALM中,并且包含两个独特的时钟源和三个时钟使能信号。

LAB控制模块使用两个时钟源和三个时钟使能信号生成高达三个时钟。每个时钟和时钟使能信号都是相连的。

置低时钟使能信号会关闭相应的全LAB(LAB-wide)时钟。

ALM输出

每个ALM中的通用布线输出驱动本地,行和列布线资源。两个ALM输出能驱动行、列或者直链布线连接,并且其中的一个ALM输出也能够驱动本地互联资源。

LUT,加法器或者寄存器输出能驱动ALM输出。LUT或加法器能够驱动一个输出,而寄存器驱动另一个输出。

寄存器封装(RegisterPacking)通过将无关的寄存器和组合逻辑封装在一个ALM中来提高器件利用率。改善布局布线的另一种机制是支持寄存器输出驱动回相同ALM的LUT中,使寄存器与其本身的扇出LUT封装在一起。ALM也能够驱动寄存的LUT以及未寄存的LUT或者加法器输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章