资料下载

使用FPGA设计数字跑表的方案和测试结果说明

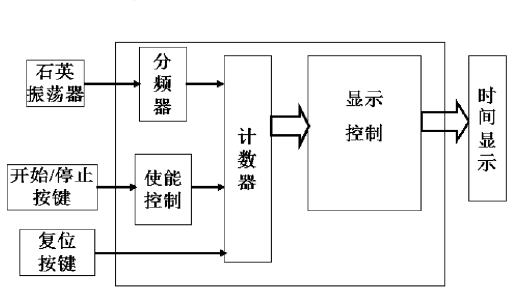

本文详细介绍了数字秒表的设计指标,设计思路,设计方案,系统电路设计,系统单元模块设计,系统硬件实现与测试的结果。

科技高度发展的今天, 集成电路和计算机应用得到了高速发展。尤其是计算机应用的发展。它在人们日常生活已逐渐崭露头角。大多数电子产品多是由计算机电路组成,如:手机、mp3等。而且将来的不久他们的身影将会更频繁的出现在我们身边。各种家用电器多会实现微电脑技术。电脑各部分在工作时多是一时间为基准的。本文就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字秒表。秒表在很多领域充当一个重要的角色。在各种比赛中对秒表的精确度要求很高,尤其是一些科学实验。他们对时间精确度达到了几纳秒级别。

本项目的任务是掌握使用VHDL语言的设计思想;熟悉ise 软件的使用;了解XILINX 学生EDA实验板。了解 EDA 技术,对计算机系统中时钟控制系统进一步了解,掌握状态机工作原理,同时了解计算机时钟脉冲是怎么产生和工作的。在掌握所学的计算机组成与结构课程理论知识时。通过对数字秒表的设计, 进行理论与实际的结合,提高与计算机有关设计能力,提高分析、解决计算机技术实际问题的能力。通过课程设计深入理解计算机结构与控制实现的技术, 达到课程设计的目标。

VHDL 的设计流程主要包括以下几个步骤:

1. 文本编辑:用任何文本编辑器都可以进行, 也可以用专用的HDL编辑环境。通常VHDL文件保存为.vhd 文件

2. 功能仿真:将文件调入 HDL 仿真软件进行功能仿真,检查逻辑功能是否正确。

3. 逻辑综合: 将源文件调入逻辑综合软件进行综合, 即把语言综合成最简的布尔表达式。逻辑综合软件会生成.edf 或.edif 的 EDA 工业标准文件。

4. 布局布线:将.edf 文件调入PLD 厂家提供的软件中进行布线,即把设分秒0.01 秒计好的逻辑安放PLD/FPGA 内。

5. 时序仿真: 需要利用在布局布线中获得的精确参数,用仿真软件验证电路的时序。(也叫后仿真) 通常以上过程可以都在 PLD/FPGA 厂家提供的开发工具。

6. 器件编程。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章