资料下载

如何实现FPGA电源的设计资料概述

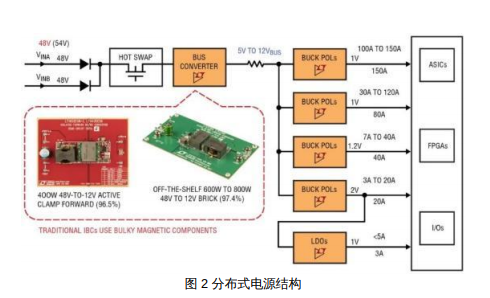

通常来说外部电源为 FPGA 或者 CPLD 内部和外部正常工作提供电能源。实施电源方案时,设计人员应该明确知道这些供电电源 ( 也称为“轨式电源” ) 的总功率。而且,和器件外部消耗的总功率相比,设计人员还需要考虑器件内部实际消耗的总功率 ( 称为“热功率”或者“耗散功率” ) ,例如,外部输出电容负载和平衡电阻匹配网络的功耗。

一、FPGA 使用的电源类型

FPGA 电源要求输出电压范围从 1.2V 到 5V,输出电流范围从数十毫安到数安培。可用三种电源:低压差(LDO)线性稳压器、开关式 DC-DC 稳压器和开关式电源模块。最终选择何种电源取决于系统、系统预算和上市时间要求。如果电路板空间是首要考虑因素,低输出噪声十分重要,或者系统要求对输入电压变化和负载瞬变做出快速响应,则应使用 LDO 稳压器。LDO 功效比较低(因为是线性稳压器),只能提供中低输出电流。输入电容通常可以降低 LDO 输入端的电感和噪声。LDO 输出端也需要电容,用来处理系统瞬变,并保持系统稳定性。也可以使用双输出 LDO,同时为 VCCINT 和 VCCO 供电。如果在设计中效率至关重要,并且系统要求高输出电流,则开关式稳压器占优势。开关电源的功效比高于 LDO,但其开关电路会增加输出噪声。与 LDO 不同,开关式稳压器需利用电感来实现 DC-DC 转换。

二、FPGA 的特殊电源要求

为确保正确上电,内核电压 VCCINT 的缓升时间必须在制造商规定的范围内。对于一些 FPGA,由于 VCCINT 会在晶体管阈值导通前停留更多时间,因此过长的缓升时间可能会导致启动电流持续较长时间。如果电源向 FPGA 提供大电流,则较长的上电缓升时间会引起热应力。ADI 公司的 DC-DC 稳压器提供可调软启动,缓升时间可以通过外部电容进行控制。缓升时间典型值在 20ms 至 100ms 范围内。许多 FPGA 没有时序控制要求,因此 VCCINT、VCCO 和 VCCAUX 可以同时上电。如果这一点无法实现,上电电流可以稍高。时序要求依具体 FPGA 而异。对于一些 FPGA,必须同时给 VCCINT 和 VCCO 供电。对于另一些 FPGA,这些电源可按任何顺序接通。多数情况下,先给 VCCINT 后给 VCCO 供电是一种较好的做法。当 VCCINT 在 0.6V 至 0.8V 范围内时,某些 FPGA 系列会产生上电涌入电流。在此期间,电源转换器持续供电。这种应用中,因为器件需通过降低输出电压来限制电流,所以不推荐使用返送电流限制。但在限流电源解决方案中,一旦限流电源所供电的电路电流超过设定的额定电流,电源就会将该电流限制在额定值以下。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章