资料下载

×

模拟CMOS的静电和过压危害如何避免

消耗积分:3 |

格式:pdf |

大小:0.16 MB |

2020-11-25

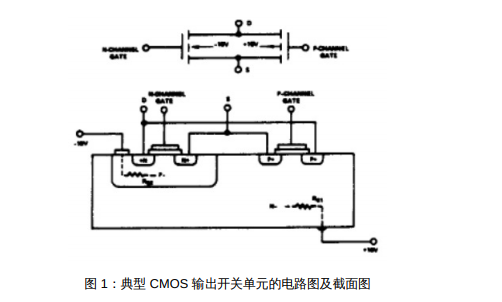

对于模拟 CMOS(互补对称金属氧化物半导体)而言,两大主要危害是静电和过压(信号电压超过电源电压)。了解这两大危害,用户便可以有效应对。

静电

由静电荷积累(V=q/C=1kV/nC/pF)而形成的静电电压带来的危害可能击穿栅极与衬底之间起绝缘作用的氧化物(或氮化物)薄层。这项危害在正常工作的电路中是很小的,因为栅极受片内齐纳二极管保护,它可使电荷损耗至安全水平。然而,在插人插座时,CMOS 器件与插座之间可能存在大量静电荷。如果插人插座的第一个引脚恰巧没有连接齐纳二极管保护电路,栅极上的电荷会穿过氧化层释放而损坏器件。以下四步有助于防止器件在系统装配阶段受损:将未使用的 CMOS 器件存放于黑色导电泡沫材料中,这样在运输时可以防止引脚之间积累电荷;负责器件接插的操作人员应通过一个塑料接地带与系统电源地相连;从防护性的泡沫材料中取出 CMOS 器件前,泡沫材料应与电源共地,释放掉积累的电荷;在电路插人电路板之后,移动电路板时应保持电路板接地或屏蔽。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章