资料下载

×

如何使用FPGA实现并行数字相关器

消耗积分:0 |

格式:rar |

大小:0.31 MB |

2021-01-26

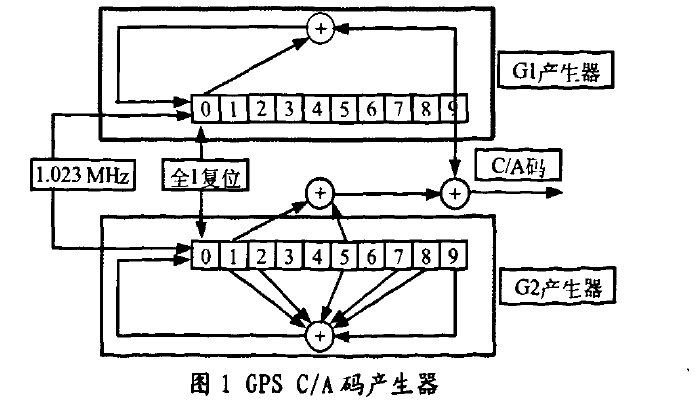

扩频码的相关解扩是扩频通信接收机的关键技术之一,主要介绍了数字相关器在全球定位系统(GPS)信号捕获中的应用,并进行了FPGA实现。在设计中,采用了16路并行相关运算的方式加快相关解扩运算速度。在GPS信号时域捕获的理论推导基础上,给出了数字下变频电路结构,分析了载波NcO的频率精度,详细讨论了扩频码相关解扩单元阵列的计算方法和电路结构与参数。最后,通过ModclSim算法仿真和Xilinx Virtex一5 LX220 FPGA测试,取得了较好的捕获效果。

扩频通信系统,即扩展频谱通信系统,其基本特点是传输信息所用信号带宽远大于信息本身带宽。直接序列扩频通信是扩频通信的主要方式,其原理是直接用具有高码速率的扩频码序列在发射端扩展信号的频谱,然后在接收端用相同的扩频码序列进行解扩,把展宽的扩频信号还原成原始信号。GPS卫星发射信号使用了直接序列扩频技术,在GPS接收机需要对扩频信号进行相关解扩。这里首先介绍GPS扩频码和中频信号的数字下变频,然后就扩频码相关解扩计算的FPGA实现进行详细讨论。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章