资料下载

使用内部PLL同步多个并行设备

ABSTRACT

The Texas Instruments family of audio converters can be used in various multichip configurations in order to realize multichannel processing using the time-division multiplexing (TDM) feature. Using a multichip solution sometimes requires synchronization of channels such that all of the devices operating in parallel operate in lock-step with each other to prevent phase shift errors between channels. The mechanisms and programming of the TLV320ADC3101 are discussed in this application report.

Introduction

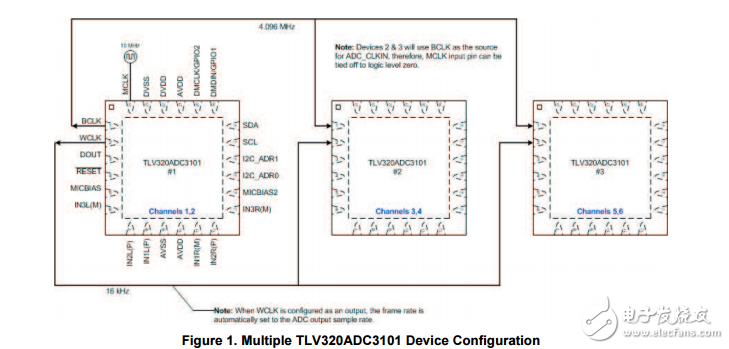

Each application for multichannel support may have different requirements having to do with selection of master clocks and synchronization. This application report specifically addresses the usage of a PLL as the master clock reference as well the programming and sequencing of instructions such that all of the parallel devices are instruction locked. The method and programming instructions used in this application report were tested using three TLV320ADC3101 evaluation modules (EVM) and its companion USB motherboard. Verification of this method and programming was performed using an Audio Precision test instrument by measuring the phase difference between each channel. The configuration in this application report uses three devices in parallel. This is an arbitrary choice and can be expanded to as many devices as needed by the application.

Clock Configuration Block Diagram Figure 1 shows that Device #1 is the master clock reference for all the other devices. Device #1 takes in an MCLK frequency that is used by the internal PLL, which in turn produces BCLK that is used by the other devices as BCLK (see Figure 31 in the TLV320ADC3101 Specification, page 26)。 The output clock rate has to be fast enough to accomplish the subsequent processing for the chosen filter algorithm.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章