资料下载

cy7c057v异步双端口RAM

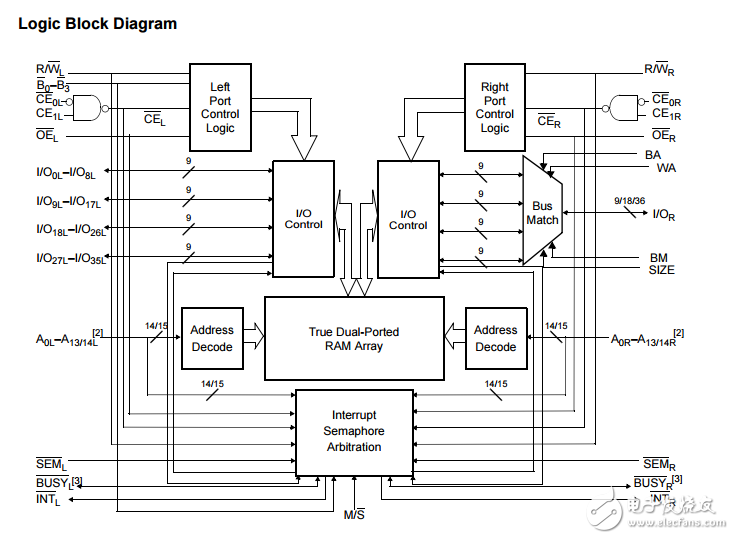

The CY7C056V and CY7C057V are low-power CMOS 16K and 32K × 36 dual-port static RAMs. Various arbitration schemes are included on the devices to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The devices can be utilized as standalone 36-bit dual-port static RAMs or multiple devices can be combined in order to function as a 72-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 72-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory. Each port has independent control pins: Chip Enable (CE) [1], Read or Write Enable (R/W), and Output Enable (OE)。 Two flags are provided on each port (BUSY and INT)。 BUSY signals that the port is trying to access the same location currently being accessed by the other port. The Interrupt Flag (INT) permits communication between ports or systems by means of a mailbox. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic Power-down feature is controlled independently on each port by Chip Select (CE0 and CE1) pins. The CY7C056V and CY7C057V are available in 144-pin TQFP and 172-ball BGA packages. For a complete list of related resources, click here.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章