资料下载

×

基于硬件加速系统的PCIe-SRIO桥的逻辑结构

消耗积分:0 |

格式:rar |

大小:1.02 MB |

2017-11-03

基于混合架构的硬件加速是计算机领域中很重要的研究方向之一。它是指将一些特定的任务从通用CPU移植到硬件处理模块上并进行相应的算法优化。由于硬件设备的专用结构,这些硬件处理模块往往比在基于顺序指令集的CPU上运行同样功能的软件在速度上有大幅度的提升。

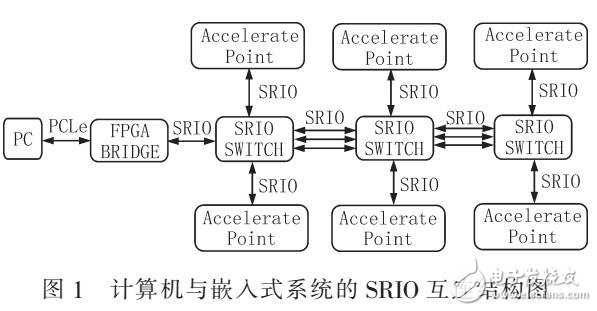

文中的主要研究内容是通用CPU和嵌入式计算硬件之间的桥接。这是硬件加速系统的关键技术问题之一,既要求较高的传输速率,也要求数据类型、长度、通道数量的灵活性。当前,计算机系统多采用PCI Express(PCIe)与外设进行数据交互。而高性能的分布式嵌入式处理系统则多采用SerialRapidl0 (SRIO)作为接口标准。实现PCIe总线到Rapidl0桥,意味着实现了通用计算机与多结点、多类型的分布式硬件计算子系统的接口能力,为硬件加速系统提供了跨架构的数据传输通道。文中介绍了一种基于FPCA的PCIe-SRIO桥接方法,在性能和功能上有效的支撑了大规模硬件加速系统的实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章